# Designing Multi-Level Resistance States in Graphene **Ferroelectric Transistors**

Morteza Hassanpour Amiri, Jonas Heidler, Klaus Müllen, Paschalis Gkoupidenis, and Kamal Asadi\*

Conventional memory elements code information in the Boolean "0" and "1" form. Devices that exceed bistability in their resistance are useful as memory for future data storage due to their enhanced memory capacity, and are also a necessity for contemporary applications such as neuromorphic computing. Here, with the aid of an experimentally validated device model, design rules are outlined and more than two stable resistance states in a graphene ferroelectric field-effect transistor are experimentally demonstrated. The design methodology can be extrapolated for on-demand introduction of multiple resistance states in ferroelectric transistors for applications both in data storage and neuromorphic computing.

#### 1. Introduction

Resistance switching in 2D-material-based ferroelectric fieldeffect transistors (Fe-FETs)[1] is achieved by modulation of charge carrier density and thereby conductance of the 2D material by polarization of the ferroelectric gate dielectric. [2-10] The binary states, "0" and "1," are programmed by switching from one polarization state to the another by applying a bias that exceeds the coercive bias,  $V_{\rm C}$ , of the ferroelectric gate. [20–23] Graphene has been the workhorse of the 2D material family. Demonstration of wafer-level upscaling of graphene Fe-FETs,[13-19] on flexible foils,[23-27] and even fully solution-processed graphene Fe-FETs<sup>[19]</sup> has supported the proposed application of 2D materials for high-speed nonvolatile memories.[11,12]

The conventional Fe-FETs have a Boolean "0" and "1" output. [28-30] The binary system is simple but offers limited data storage capacity as every bit of information (0 and 1) is translated to one of the two possible states. Multi-valued storage devices have been proposed to alleviate the limited storage capacity of the binary

M. Hassanpour Amiri, J. Heidler, Prof. K. Müllen, Dr. P. Gkoupidenis, Humboldt Research Group

Max-Planck Institute for Polymer Research Ackermannweg 10, Mainz 55128, Germany E-mail: asadi@mpip-mainz.mpg.de

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/adfm.202003085.

© 2020 The Authors. Published by WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

DOI: 10.1002/adfm.202003085

devices.[31,32] For instance, in a quaternary memory, the information is coded into one of the four possible states of 0, 1, 2, and 3 that together represent the information of two binary bits and are represented by 00, 01, 10, and 11, respectively. In comparison, for a 16 × 16 bit array, the binary system offers 256 bits, offering 2256 possible states, while at the same time, the quaternary system offers  $4^{256}$  (or  $(2^{256})^2$ ) possible states. A quaternary graphene Fe-FET would require four different conductance levels at zero gate bias. Despite the technological promise, multi-bit 2D material Fe-FETs have not been extensively studied.[12,32,33]

Memory devices also play central role in the hardware-based implementation of artificial neural networks (ANNs).[45] The figure of merit in this hardware-based approach is the mapping of the coupling between neurons that are found in biology (also known as synaptic weight) in the device memory state. [46] This synaptic weight is usually regarded as a continuous variable in biology, and therefore it is more biologically realistic to be emulated with analogue memory devices. [47] It is now wellknown that core functions of ANNs, such as vector-matrixmultiplication, can be implemented on a crossbar array of analogue memory devices. [47-50] Despite the fact that nowadays research is quite intense in the field of analogue memory devices for synaptic electronics, the representation of synaptic weight with lower precision (i.e., few bit-memory) is still a viable route for the implementation of ANNs.<sup>[51,52]</sup> This approach represents a trade-off between precision in synaptic weight mapping and data volume during transfer,[49] and even allows for the potential implementation of hardware-based ANNs with devices that lack intrinsic analogue memory phenomena. Among other devices, a few examples of 2D or semiconductor Fe-FETs that exhibit gradual modulation of resistance have been reported in the past.[53-56] However, specific design principles for on-demand introduction of the number of states in Fe-FETs based on the needs of a specific application have not been reported yet.

Here, we design and experimentally demonstrate graphene Fe-FETs with four resistance states (quaternary) and generalize the design to exceed four states in a graphene Fe-FET. The Fe-FETs are realized with graphene grown from chemical vapor deposition (CVD) technique that are gated with a ferroelectric polymer poly(vinylidenefluoride-co-trifluoroethylene) (P(VDF-TrFE)). We hypothesize that the methodology developed can be used for any combination of 2D materials with both organic and inorganic ferroelectrics, provided that the correct material

www.afm-journal.de

www.advancedsciencenews.com

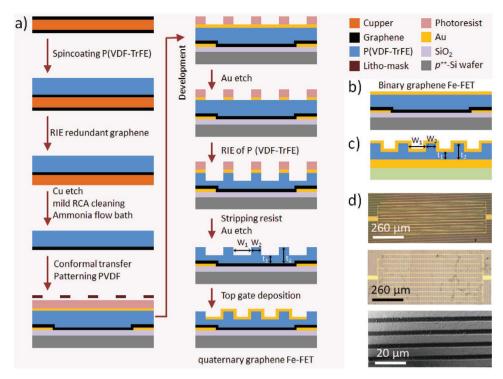

**Figure 1.** a) Process flowchart of quaternary graphene Fe-FETs. b) Schematic of a conventional binary graphene Fe-FET. c) Cross-sectional schematics of the patterned P(VDF-TrFE) capacitors. d) Optical photograph of the graphene/P(VFD-TrFE) layer that is transferred on to prefabricated interdigitated Au electrodes with (top) pattern parallel and (middle) perpendicular to the graphene channel. Bottom: SEM image of the patterned P(VDF-TrFE) layer.

description is taken into consideration. The methodology allows for developing memory cells with multiple number of states that are predefined through design. The results provide valuable guidelines for realization of multi-level ferroelectric transistors for applications ranging from data storage to neuromorphic computing.

## 2. Experimental Section

CVD graphene grown on copper (Graphenea) was coated with P(VDF-TrFE) (65-35% mole %) (Solvay). A layer of P(VDF-TrFE), with thickness of 800-1500 nm, was spin-coated onto the graphene-coated copper foil from a 10 wt% methyl ethyl ketone (Sigma-Aldrich) solution. Doping-free transfer of the graphene was done according to previous reports.<sup>[58]</sup> The graphene layer on the uncoated copper surface was removed by oxygen plasma. After etching Cu in 1 M aqueous bath of FeCl<sub>3</sub>, the floated graphene/P(VDF-TrFE) layer was thoroughly washed using deionized (DI) water and a continuous flow bath of NH<sub>3</sub>:DI-water (1 M) for 30 min. Subsequently, the graphene/ P(VDF-TrFE) layer was transferred on to the pre-patterned FET substrate using the conformal transfer technique. The interdigitated Ti/Au (2 nm/150 nm) source-drain electrodes with a fixed channel width of 10 000 µm and a varying channel length of 10-40 µm, Figure 1d were fabricated by conventional photolithography on 6 in. Si wafers with 250 nm hexamethyldisilazane-passivated, thermally grown SiO<sub>2</sub>.

The stack was dried at 40 °C for 12 h in a vacuum oven at 1 mbar, and then annealed at 140 °C for 2 h to enhance

crystallinity of the P(VDF-TrFE) layer. The fabrication process of Fe-FET was completed by evaporation of a 100 nm gold top gate electrode through a shadow mask.

Patterned P(VDF-TrFE) layers for capacitors and gate structures, Figure 1c, were realized by performing an additional photolithography step. A layer of Au was deposited onto the P(VDF-TrFE) film and patterned. The underlying Au electrode lines were used as a cue for the alignment of the top patterns. It was noted that a slight misalignment of the etching lines with the Au contact lines would not affect the experimental observation. For down-scaled device, proper alignment of the pattern with the electrodes is required. Patterns parallel and perpendicular to the graphene channel, as shown in Figure 1d, were realized. The exposed Au stripes were etched in KI/I<sub>2</sub>/H<sub>2</sub>O (4:1:4) solution. Subsequently, the exposed P(VDF-TrFE) was etched using reactive ion etching (RIE) with a plasma power of 150 W, at a pressure of 0.08 mbar, and oxygen/Ar flow of 30/10 sccm (etching rate of 330 nm s<sup>-1</sup>). The etching depth was controlled by RIE etching time. Note that the etching rate was chosen due to the large thickness of the P(VDF-TrFE) layer. For thinner P(VDF-TrFE) films, required in application, the etching rate should be substantially lower to allow for good control of the etching depth. After the etching process, the redundant photoresist and Au cover layer were stripped and etched, and the substrates were thoroughly rinsed in DI water. The photoresist was removed after the RIE process because the resist remover solvent dissolves P(VDF-TrFE) layer. Patterned graphene Fe-FETs and capacitors were finalized by evaporation of a top Au electrode (150 nm). The flow chart of the fabrication process is given in Figure 1a. Trenches are patterned parallel to

www.advancedsciencenews.com

ADVANCED FUNCTIONAL MATERIALS

the interdigitated electrodes (Figure 1d). All electrical measurements were performed in high vacuum (10<sup>-6</sup> mbar) using a Keithley 4200 semiconductor characterization system. The Fe-FET measurements were performed by application of a small bias of +50 mV to the drain, and the drain current was monitored while changing the gate bias. The retention measurements of the programmed states in Fe-FETs were performed at zero gate bias while a bias of +50 mV was applied to the drain.

## 2.1. Multi-Bit Graphene Memory through Design

An analytical model was previously developed that coupled voltage-dependent charge displacement of the ferroelectric gate layer with the charge transport across the graphene channel. [57] To extend the formalism to multi-bit graphene Fe-FET, the geometrical topography was incorporated in the charge displacement description of the ferroelectric gate layer. The displacement, D, of a ferroelectric gate layer with a constant thickness, t, is the sum of the linear dielectric response and the ferroelectric polarization and is given by

$$D = \varepsilon_0 \varepsilon_P E + P(V, t) \tag{1}$$

where E(=V/t) and P(V) are the electric field and ferroelectric polarization, respectively. Voltage-dependent polarization of the ferroelectrics can be described phenomenologically using

$$P^{+}(V,t) = \varepsilon_0 \varepsilon_P \frac{V}{t} + \frac{P_2}{2} f(V,t)$$

(2)

with

$$f(V,t) = \left(\tanh\left(\frac{V+V_{c}}{t\delta}\right) + \tanh\left(\frac{V-V_{c}}{t\delta}\right)\right)$$

(3)

and

$$\delta = 2\frac{V_c}{t} \left[ \ln \left( \frac{1 + P_r / P_s}{1 - P_r / P_s} \right) \right]^{-1} \tag{4}$$

$\left. \frac{P_{\rm r}/P_{\rm S}}{P_{\rm r}/P_{\rm S}} \right) \right] \tag{4}$

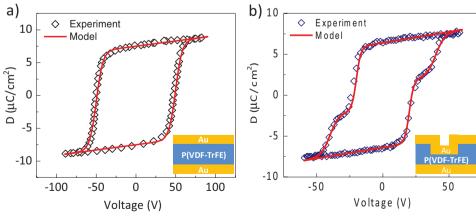

where  $V_c$ ,  $P_s$ , and  $P_r$  are the coercive bias, saturation polarization, and remanent polarization of the ferroelectric layer, respectively. The  $P^+(V)$  functional denotes the lower branch of the polarization loop, going from negative bias and polarization towards the positive values. The negative branch,  $P^-(V)$ , is calculated using  $P^-(V) = -P^+(-V)$ . Equation (2) describes the D-V loop of an unpatterned P(VDF-TrFE) ferroelectric capacitor with a good accuracy, as shown in **Figure 2a**. [39-44] The best fit is obtained using the following parameter values:  $\varepsilon_P = 15$ ,  $P_r = 75.09$  mC m<sup>-2</sup>,  $P_S = 75.1$  mC m<sup>-2</sup>, and  $E_C = (V_c/t) = 60$  MV m<sup>-1</sup>, which are the typical, experimentally reposted values for P(VDF-TrFE).

Writing the P(V) functional in terms of voltage allows for generalizing the formalism for the patterned P(VDF-TrFE) capacitor as follows

$$P^{+}(V) = \sum_{i=1,2} (W_{i} \times P(V_{i}, t_{i}))$$

(5)

where  $W_i$  and  $t_i$  are areal fraction and thickness (nm) of the respective fraction of the patterned P(VDF-TrFE) film, as schematically shown in Figure 1c. Capacitors with various fractional areas were tested. Representative experimental D-V loop of a capacitor with  $W_1=0.25$  and  $W_2=0.75$  is shown in Figure 2b. Using Equation (5) and the parameters resulting from the fit to Figure 2a, combined with the geometrical parameters of  $(W_1, t_1) = (0.25, 400 \text{ (nm)})$  and  $(W_2, t_2) = (0.75, 800 \text{ (nm)})$ , a good description of the D-V loop was obtained for the patterned P(VDF-TrFE) capacitor as shown in Figure 2b.

The polarization of the ferroelectric gate layer changes the effective gate bias experienced by the graphene layer

$$V_{\text{eff}} = V_{\text{G}} - V_{\text{D}} + \frac{P^{\pm}(V_{\text{G}})}{C_{P}}$$

(6)

where  $V_G$  and  $V_D$  represent gate and Dirac voltage, respectively,  $\frac{P^\pm(V_G)}{C_P}$  is the polarization-induced voltage, and  $C_P$  is the geometrical areal capacitance of the P(VDF-TrFE) gate layer in F m<sup>-2</sup>. Assuming that the remanent and saturated polarization of the ferroelectric gate in Fe-FET remains the same as those in the capacitor, and 100% coupling of the ferroelectric polarization

Figure 2. D–V loop of ferroelectric capacitors (insets) with a) a uniform and b) patterned P(VDF-TrFE) films. The solid red lines show the fits produced by the phenomenological model.

www.advancedsciencenews.com www.afm-ioi

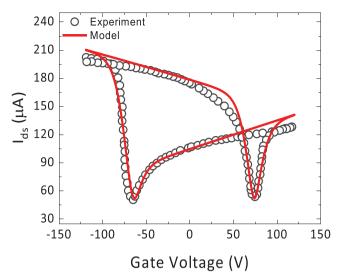

**Figure 3.** Transfer characteristics of a graphene Fe-FET with unpatterned plane P(VDF-TrFE) gate layer. The solid line shows the fit obtained using the analytical device model.

with channel conductance, hence ignoring depolarization,<sup>[37]</sup> the gate bias-dependent carrier density can be written as

$$n(V_{G}) = \frac{C_{P}}{e} \left( V_{eff} + \frac{b^{2}}{2e} C_{P} - b \left( \frac{V_{eff} C_{P}}{e} + \frac{b^{2}}{4e^{2}} C_{P}^{2} \right)^{\frac{1}{2}} \right)$$

(7)

where  $b=\frac{\hbar v_f\sqrt{\pi}}{2e}$  appears due to taking into account the quantum capacitance of the graphene layer,  $(2e^2\sqrt{n(V_{\rm G})})/(\hbar v_f\sqrt{\pi})$  with  $\hbar$  and  $v_f$  are reduced Plank's constant and Fermi velocity of the carriers, respectively. The source-drain current,  $I_{\rm ds}$ , in the graphene Fe-FET is then given by

$$I_{\rm ds}(V_{\rm G}) = V_{\rm ds} \times \left( R_{\rm c} + N_{\rm sq} \left( \mu e \sqrt{n_0^2 + n(V_{\rm G})^2} \right)^{-1} \right)^{-1}$$

(8)

where  $R_{\rm c}$ ,  $N_{\rm sq}$ , and  $\mu$  are contact resistance of the metal-graphene junction, number of squares of the gated area, and charge carrier mobility of the graphene layer, respectively.

The model was experimentally validated by fitting the transfer curves for the graphene Fe-FETs with a plane,

unpatterned P(VDF-TrFE) gate layer. The parameters obtained from the fits of the D–V loops of the P(VDF-TrFE) capacitor, Figure 2a, were used as the input parameters for the gate layer of the Fe-FETs. The model accurately describes the transfer characteristics of the graphene Fe-FET with constant mobility of  $\mu$  = 800 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and  $V_D$  = 285 V, as shown in Figure 3. The model describes well the Fe-FETs with unpatterned gate, and is therefore experimentally validated.

Based on the model, the operation of the graphene Fe-FET with a plane, unpatterned ferroelectric layer can now be accurately explained. Application of -125 V to the gate sets the P(VDF-TrFE) gate to its full positive polarization state, which is accompanied by accumulation of holes in the graphene channel. The hole current is persistent upon sweeping the gate bias toward zero and then further to positive gate bias. At  $\approx$ +75 V, the gate bias reaches + $E_c$ , and P(VDF-TrFE) reverses its polarization. The negative polarization state is fully compensated by electron accumulation in the graphene channel, and the electron current prevails as the gate voltage increases further toward +125 V. The electron current persists upon sweeping back the gate bias to zero and down towards negative biases. At nearly  $\approx$ -75 V, the gate bias reaches  $-E_c$  and the polarization of the P(VDF-TrFE) gate layer switches back to the initial positive polarization state, re-establishing the hole current. The presence of both electron and hole channels in the graphene Fe-FET is due to the ambipolarity of the CVD-graphene layer by removal of the unintentional doping.<sup>[58]</sup>

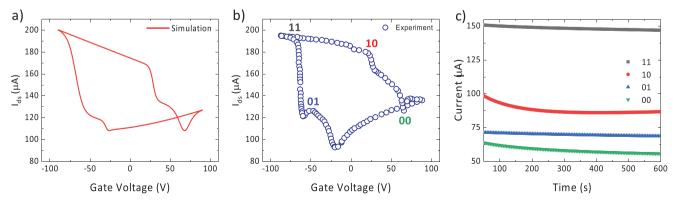

Following the experimental validation, the model is used to make predictions for Fe-FETs with patterned gates. To produce transfer curves, the parameters that are obtained for the graphene Fe-FET with un-patterned P(VDF-TrFE) gate are used. The transfer characteristics are calculated for the patterned structure perpendicular to the graphene channel by varying the factional area of  $W_1$  (and  $W_2$ ) from 0 to 0.50. A representative calculated D-V loop is given in Figure 2b for  $W_1 = 0.25$  and  $W_2 = 0.75$ . The calculated transfer characteristics of the comprising graphene Fe-FETs with the same patterned P(VDF-TrFE) are shown in Figure 4a. The Fe-FET clearly shows four different conductance levels depending on the polarization configuration of the patterned gate layer. Due to the ambipolarity of the graphene layer, the intermediate polarization states are compensated and therefore stable in time, hence no depolarization of the gate layer is expected.[32,34]

Figure 4. a) Model prediction of the quaternary graphene Fe-FET and b) experimental demonstration of the same device using a patterned P(VDF-TrFE) ferroelectric gate. c) Retention time of different states of the quaternary graphene Fe-FET measured at zero gate bias and a drain bias of +50 mV.

The experimental transfer characteristics of the graphene Fe-FETs with patterned P(VDF-TrFE) perpendicular to the graphene channel is shown in Figure 4b. The P(VDF-TrFE) layer has the same pattern ( $W_1 = 0.25$  and  $W_2 = 0.75$ ) with a thickness of  $t_1 = 600$  nm and  $t_2 = 1200$  nm, respectively. Application of negative gate bias of -90 V sets the patterned P(VDF-TrFE) layer in the fully positive polarization state, and hole accumulation is formed in the graphene layer. Upon sweeping the gate bias towards positive biases, the drain current shows a sudden drop at a gate bias of ≈+30 V. The thin part of the P(VDF-TrFE) gate layer is now in negative polarization state. As gate bias approaches nearly +60 V, the thick part of the P(VDF-TrFE) layer is now in positive polarization state, and therefore the P(VDF-TrFE) layer is homogeneously in positive polarization. As a result, a uniform electron accumulation channel is formed in the graphene layer. Upon back sweeping the gate bias, the electron current persists. At a gate bias of ≈-30 V, the hole accumulation channel is partly retrieved. At gate bias -60 V, P(VDF-TrFE) gate layer is again in full negative polarization. The Fe-FET, depending on the programming of the gate layer, shows four different conductance levels that are stable in time as shown in Figure 4c, in the absence of the external gate bias. Therefore, the graphene Fe-FET has a quaternary output.

The Fe-FETs with parallel alignment of the pattern with respect to the graphene channel have shown similar transfer characteristics. A parallel alignment would yield series connection of the channel portions, where the highest resistive portion of the channel would dominate the transfer characteristics. The perpendicular alignment would produce channels that are connected in parallel, and where the currents add up. In

the case of graphene, the difference between the high and low resistance states, as shown in Figure 3, is a factor of two, which apparently is not large enough to yield different transfer characteristics. Dissimilarity between the two alignments is expected when more resistive semiconductors than graphene are used.

It should be noted that for a relatively large-area device, where the ferroelectric layer is composed of many domains. Multi-level resistance<sup>[61,62]</sup> can also be realized by partial polarization of the ferroelectric layer into its intermediate polarization states<sup>[59,60]</sup> using a pulsing scheme. However, downscaling of the devices as eventually needed for neuromorphic applications can limit multi-value resistance. At device dimensions comparable with ferroelectric domain size, partial polarization of the ferroelectric layer, as to produce multi-levels of resistance, becomes challenging.<sup>[63]</sup> However, for a patterned ferroelectric gate, the precise control over the polarization, and therefore channel conductance, is straightforward, whereas for partial polarization, precise control of the polarization level can become challenging.

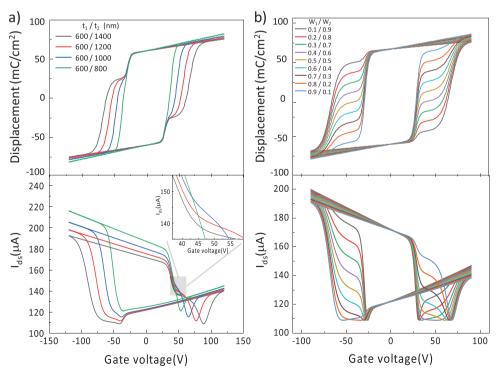

Realization of differentiable intermediate "01" and "10" states depends very much on the geometrical features, that is, the height and width of the pattern in the ferroelectric layer. To investigate the effect of the geometry on the transfer curve of the Fe-FET, both height and width are varied. In Figure 4a, the effect of variation in the height for a fixed  $W_1/W_2$  of 0.25/0.75 is shown. The intermediate regime becomes more apparent as the height difference increases, as highlighted for the enlarged section of the transfer curve, where state "10" emerges. Since almost all ferroelectric thin-films are polycrystalline, they have a distributed coercive voltage. As a result, a

**Figure 5.** The effect of height and width of the patterns in the ferroelectric gate layer on the transfer characteristics of the graphene Fe-FET. a) The influence of different thickness for  $W_1/W_2$  of 0.25/0.75 and b) the effect of the width for  $t_1/t_2$  of 600/1200 nm.

ADVANCED FUNCTIONAL MATERIALS

single switching voltage is absent and there is always a voltage distribution around  $V_{\rm c}$ . For the Fe-FETs with patterned gate to have differentiable intermediate state, the height difference should be large enough to ensure that the  $V_{\rm c1}$  and  $V_{\rm c2}$  are well-separated and do not overlap. Therefore, as a design guide, an optimal height difference of 50% is suggested for clearly discernable "01" and "10" intermediate states in the transfer characteristics of the Fe-FET.

The influence of the width of the patterns on the transfer curve is presented in Figure 4b for a fixed height difference of 50%, and variable ratio of  $W_1/W_2$ . Changes in W have a distributing effect on the polarization, and consequently the current level of the intermediate "01" and "10" states. The minimum  $W_1$ , an important factor for downscaling of the patterned devices, could be as small as tens of nanometers because it was demonstrated that the ferroelectric domain can be stabilized down to tens of nanometer. [65]

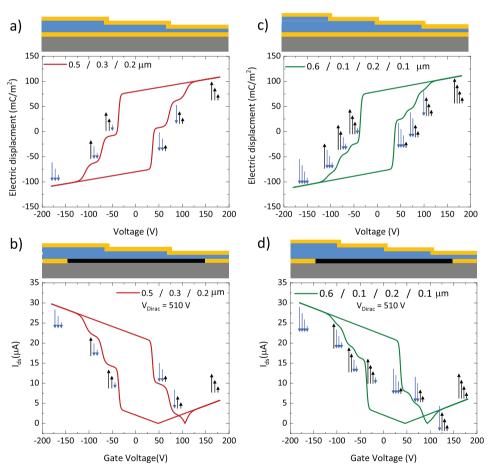

The methodology of patterning the ferroelectric gate defines various switching voltages that allow for creating multiple number of resistance states that can be controlled deterministically. As a demonstration, the designs are provided for

capacitors with three and four steps in the thickness of the ferroelectric layer, as presented in Figure 6a-c, respectively. The details of the design, namely the thicknesses and the fractional areal coverage of every thickness, are given in the legends of the Figure 6. Three steps in the ferroelectric film topography lead to six different polarization states, as shown in Figure 5a. Implementation of the ferroelectric layer as the gate insulator yields a Fe-FET that clearly shows six different resistance states. as shown in Figure 6b. Similarly, four steps in the ferroelectric film topography leads to eight different polarization states, Figure 5b, and consequently eight different resistance states in the Fe-FET, as shown in Figure 6d. It should be noted that the intermediate states are determined by measuring the current at zero gate bias, not at the coercive bias of the intermediate states. Since polarization of the intermediate states is compensated and, therefore, stabilized, the current level of the intermediate states will be, therefore, different and the intermediate states can be easily differentiated from one another.

A brief note should be given about the switching voltages in multi-level resistance states in patterned graphene Fe-FETs. For many applications, including memory and neuromorphic,

Figure 6. a) Schematic of ferroelectric layer with three topographic steps (top) and the simulated corresponding displacement–voltage characteristics in a capacitor (bottom). b) Schematic of ferroelectric transistor with three topographic steps (top) and the simulated corresponding transfer characteristics (bottom), clearly demonstrating six different resistance levels. c) Schematic of ferroelectric layer with four topographic steps (top) and the simulated corresponding displacement–voltage characteristics in a capacitor (bottom). d) Schematic of ferroelectric transistor with four topographic steps (top) and the simulated corresponding transfer characteristics (bottom), clearly demonstrating eight different resistance levels. The first row of the legend in every panel shows the fractional areal coverage for different thicknesses that are given in the second row below it.

www.advancedsciencenews.com

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

[1] Y. J. Doh, G. C. Yi, Nanotechnology **2010**, 21, 105204.

- [2] I. Jung, J. Y. Son, Carbon 2012, 50, 3854.

- [3] H. S. Lee, S. W. Min, M. K. Park, Y. T. Lee, P. J. Jeon, J. H. Kim, S. Ryu, S. Im, Small 2012, 8, 3111.

- [4] Y. T. Lee, D. K. Hwang, W. K. Choi, J. Korean Phys. Soc. 2016, 69, 1347.

- [5] G. D. Belletti, S. D. Dalosto, S. Tinte, J. Phys.: Condens. Matter 2016, 28, 435002.

- [6] Y. Chen, X. Wang, P. Wang, H. Huang, G. Wu, B. Tian, Z. Hong, Y. Wang, S. Sun, H. Shen, ACS Appl. Mater. Interfaces 2016, 8, 32083.

- [7] X. Wang, C. Liu, Y. Chen, G. Wu, X. Yan, H. Huang, P. Wang, B. Tian, Z. Hong, Y. Wang, 2D Mater. 2017, 4, 025036.

- [8] C. Yin, X. Wang, Y. Chen, D. Li, T. Lin, S. Sun, H. Shen, P. Du, J. Sun, Nanoscale 2018, 10, 1727.

- [9] D. Li, X. Wang, Y. Chen, S. Zhu, F. Gong, G. Wu, C. Meng, L. Liu, L. Wang, T. Lin, *Nanotechnology* 2018, 29, 105202.

- [10] H. J. Hwang, J. H. Yang, Y. G. Lee, C. Cho, C. G. Kang, S. C. Kang, W. Park, B. H. Lee, *Nanotechnology* 2013, 24, 175202.

- [11] H. Zhang, Y. Chen, S. Ding, J. Wang, W. Bao, D. W. Zhang, P. Zhou, Nanotechnology 2018, 29, 244004.

- [12] F. A. McGuire, Y. C. Lin, K. Price, G. B. Rayner, S. Khandelwal, S. Salahuddin, A. D. Franklin, *Nano Lett.* 2017, 17, 4801.

- [13] D. Jin, A. Kumar, K. H. Fung, J. Xu, N. X. Fang, Appl. Phys. Lett. 2013, 102, 201118.

- [14] X. Wang, P. Wang, J. Wang, W. Hu, X. Zhou, N. Guo, H. Huang, S. Sun, H. Shen, T. Lin, Adv. Mater. 2015, 27, 6575.

- [15] C. Baeumer, D. Saldana-Greco, J. M. P. Martirez, A. M. Rappe, M. Shim, L. W. Martin, Nat. Commun. 2015, 6, 6136.

- [16] Y. Zheng, G. X. Ni, C. T. Toh, M. G. Zeng, S. T. Chen, K. Yao, B. Özyilmaz, Appl. Phys. Lett. 2009, 94, 163505.

- [17] Y. L. Lee, S. Kim, C. Park, J. Ihm, Y. W. Son, ACS Nano 2010, 4, 1345.

- [18] Y. Zheng, G.-X. Ni, C.-T. Toh, C.-Y. Tan, K. Yao, B. Özyilmaz, Phys. Rev. Lett. 2010, 105, 166602.

- [19] S. Raghavan, I. Stolichnov, N. Setter, J. S. Heron, M. Tosun, A. Kis, Appl. Phys. Lett. 2012, 100, 023507.

- [20] S. Lee, Y. Lee, Carbon 2018, 126, 176.

- [21] M. Dragoman, M. Modreanu, I. M. Povey, A. Dinescu, D. Dragoman, A. Di Donato, E. Pavoni, M. Farina, *Nanotechnology* 2018, 29, 425204.

- [22] M. Zhu, J. Wu, Z. Du, R. Y. Tay, H. Li, B. Özyilmaz, E. H. T. Teo, Nanoscale 2015, 7, 14730.

- [23] Y. Zheng, G.-X. Ni, S. Bae, C.-X. Cong, O. Kahya, C.-T. Toh, H. R. Kim, D. Im, T. Yu, J. H. Ahn, EPL 2011, 93, 17002.

- [24] W. Lee, O. Kahya, C. T. Toh, B. Özyilmaz, J. H. Ahn, Nanotechnology 2013, 24, 475202.

- [25] G. X. Ni, Y. Zheng, S. Bae, C. Y. Tan, O. Kahya, J. Wu, B. H. Hong, K. Yao, B. Özyilmaz, ACS Nano 2012, 6, 3935.

- [26] X. Wang, M. Tang, Y. Chen, G. Wu, H. Huang, X. Zhao, B. Tian, J. Wang, S. Sun, H. Shen, Opt. Quantum Electron. 2016, 48, 345.

- [27] J. Heidler, S. Yang, X. Feng, K. Müllen, K. Asadi, Solid-State Electron. 2018, 144, 90.

- [28] A. Rajapitamahuni, J. Hoffman, C. H. Ahn, X. Hong, Nano Lett. 2013, 13, 4374.

- [29] E. B. Song, B. Lian, S. Min Kim, S. Lee, T. K. Chung, M. Wang, C. Zeng, G. Xu, K. Wong, Y. Zhou, Appl. Phys. Lett. 2011, 99, 042109.

- [30] H. Wang, Y. Wu, C. Cong, J. Shang, T. Yu, ACS Nano 2010, 4, 7221.

- [31] J. F. Scott, Science 2007, 315, 954.

- [32] a) P. Zubko, D. J. Jung, J. F. Scott, J. Appl. Phys. 2006, 100, 114112;

b) S. Oh, H. Hwang, I. K. Yoo, APL Mater. 2019, 7, 091109.

- [33] M. H. Yusuf, B. Nielsen, M. Dawber, X. Du, Nano Lett. 2014, 14, 5437.

- [34] W. Jie, J. Hao, Nanoscale 2018, 10, 328.

- [35] Y. L. Sun, D. Xie, J. L. Xu, X. M. Li, C. Zhang, R. X. Dai, X. Li, X. J. Meng, H. W. Zhu, Carbon 2016, 96, 695.

- [36] R. C. G. Naber, K. Asadi, P. W. M. Blom, D. M. De Leeuw, B. De Boer, Adv. Mater. 2010, 22, 933.

low-voltage operation of the resistance switching devices is required. The demonstrated patterned graphene Fe-FET operates at rather large voltages, because the primary goal is to demonstrate multi-level resistance switching and to establish the device physics. Nonetheless, the switching voltage of P(VDF-TrFE)-based memory devices could be reliably reduced to sub-3 V<sup>[38]</sup> upon reducing the thickness to below 20 nm. Therefore, low-voltage operation for the patterned Fe-FET could be realized by preparation of thinner P(VDF-TrFE) gate layers, which necessitated adoption of the P(VDF-TrFE) etching process to low etch rates.

## 3. Conclusion

Using an experimentally validated device model, we have outlined design rules for a quaternary graphene Fe-FET and experimentally demonstrated four stable resistance states of the designed graphene Fe-FET. By introducing a well-defined topographical pattern in the ferroelectric layer, four different switching voltages appear that enable programming of the gate polarization into four different states simply by application of an appropriate gate bias. We have predicted transistors with six and eight different deterministic resistance states. Based on the insight gained from the model, we propose introducing several trenches with various thicknesses within the ferroelectric gate layer to achieve multiple (>2) resistance states in a single transistor with deterministic resistance switching voltages. The device model presented here is generic, and can be adopted for graphene Fe-FETs that are fabricated with inorganic ferroelectrics or dual-gate ferroelectric transistor.<sup>[64]</sup> Analytical description for the dielectric displacement of the ferroelectric gate layer renders the proposed model applicable to other Fe-FETs based on various 2D materials. When the electrostatic description of the gate is coupled with an appropriate charge transport model, the model can determine the best operational conditions for the Fe-FETs based on the 2D material under study.

# Acknowledgements

M.H.A. and J.H. contributed equally to this work. The authors would like to acknowledge the financial support from both Alexander von Humboldt Foundation through Sofja Kovalevskaja Award and Max-Planck Institute for Polymer Research; Prof. Paul W. M. Blom for fruitful discussion; and the technical assistance of M. Beuchel, F. Keller and C. Bauer.

#### **Conflict of Interest**

The authors declare no conflict of interest.

## **Keywords**

field-effect transistors, graphene, multi-bit memory, neuromorphic computing

Received: April 7, 2020 Revised: April 21, 2020 Published online:

www.advancedsciencenews.com www.afm-journal.de

\_\_\_\_MATERIALS

- [37] K. Asadi, E. C. Timmering, T. C. T. Geuns, A. Pesquera, A. Centeno, A. Zurutuza, J. H. Klootwijk, P. W. M. Blom, D. M. De Leeuw, ACS Appl. Mater. Interfaces 2015, 7, 9429.

- [38] a) M. Li, I. Katsouras, K. Asadi, P. W. M. Blom, D. M. De Leeuw, Appl. Phys. Lett. 2013, 103, 072903; b) R. C. G. Naber, P. W. M. Blom, A. W. Marsman, D. M. de Leeuw, Appl. Phys. Lett. 2004, 85, 2032; c) R. C. G. Naber, B. de Boer, P. W. M. Blom, D. M. de Leeuw, Appl. Phys. Lett. 2005, 87, 203509; d) M. Li, N. Stingelin, J. J. Michels, M.-J. Spijkman, K. Asadi, R. Beerends, F. Biscarini, P. W. M. Blom, D. M. de Leeuw, Adv. Funct. Mater. 2012, 22, 2750; e) M. Kumar, D. G. Georgiadou, A. Seitkhan, K. Loganathan, E. Yengel, H. Faber, D. Naphade, A. Basu, T. D. Anthopoulos, K. Asadi, Adv. Electron. Mater. 2020, 6, 1901091.

- [39] R. C. G. Naber, J. Massolt, M. Spijkman, K. Asadi, P. W. M. Blom, D. M. De Leeuw, Appl. Phys. Lett. 2007, 90, 113509.

- [40] S. L. Miller, J. R. Schwank, R. D. Nasby, M. S. Rodgers, J. Appl. Phys. 1991, 70, 2849.

- [41] J. J. Brondijk, K. Asadi, P. W. M. Blom, D. M. de Leeuw, J. Polym. Sci., Part B: Polym. Phys. 2012, 50, 47.

- [42] K. Asadi, P. W. M. Blom, D. M. De Leeuw, Appl. Phys. Lett. 2011, 99, 053306.

- [43] S. Kim, J. Nah, I. Jo, D. Shahjerdi, L. Colombo, Z. Yao, E. Tutuc, S. K. Banerjee, Appl. Phys. Lett. 2009, 94, 062107.

- [44] F. Xia, V. Perebeinos, Y. M. Lin, Y. Wu, P. Avouris, Nat. Nanotechnol. 2011, 6, 179.

- [45] G. W. Burr, Nat. Mach. Intell. 2019, 1, 10.

- [46] S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, W. Lu, Nano Lett. 2010, 10, 1297.

- [47] Z. Wang, H. Wu, G. W. Burr, Nat. Rev. Mater. 2020, 5, 173.

- [48] M. Prezioso, F. Merrikh-Bayat, B. Hoskins, G. C. Adam, K. K. Likharev, D. B. Strukov, *Nature* 2015, 521, 61.

- [49] H. Tsai, S. Ambrogio, P. Narayanan, R. M. Shelby, G. W. Burr, J. Phys. D: Appl. Phys. 2018, 51, 3001.

- [50] S. Ambrogio, P. Narayanan, H. Tsai, R. M. Shelby, Boybat, C. di Nolfo, S. Sidler, M. Giordano, M. Bodini, N. C. P. Farinha, B. Killeen, C. Cheng, Y. Jaoudi, G. W. Burr, *Nature* 2018, 558, 60.

- [51] M. Courbariaux, Y. Bengio, J. P. David, in Advances in Neural Information Processing Systems 28 (Eds: C. Cortes, N. D. Lawrence, D. D. Lee, M. Sugiyama, R. Garnett), Curran Associates, Inc., New York 2015, p. 3123.

- [52] W. Tang, G. Hua, L. Wang, presented at Proc. of the Thirty-First AAAI Conf. on Artificial Intelligence, San Francisco, CA February 2017

- [53] B. Tian, L. Liu, M. Yan, J. Wang, Q. Zhao, N. Zhong, P. Xiang, L. Sun, H. Peng, H. Shen, T. Lin, B. Dkhil, X. Meng, J. Chu, X. Tang, C. Duan, Adv. Electron. Mater. 2019, 5, 1800600.

- [54] Y. Chen, Y. Zhou, F. Zhuge, B. Tian, M. Yan, Y. Li, Y. He, X. S. Miao, npj 2D Mater. Appl. 2019, 3, 31.

- [55] E. J. Kim, K. A. Kim, S. M. Yoon, J. Phys. D: Appl. Phys. 2016, 49, 075105

- [56] S. M. Yoon, S. Yang, C. W. Byun, S. W. Jung, M. K. Ryu, S. H. K. Park, B. Kim, H. Oh, C. S. Hwang, B. G. Yu, Semicond. Sci. Technol. 2011, 26, 034007.

- [57] M. Hassanpour Amiri, J. Heidler, K. Müllen, K. Asadi, ACS Appl. Electron. Mater. 2020, 2, 2.

- [58] M. Hassanpour Amiri, J. Heidler, A. Hasnain, S. Anwar, H. Lu, K. Müllen, K. Asadi, RSC Adv. 2020, 10, 1127.

- [59] T. C. Macleod, T. A. Philips, F. D. Ho, Integr. Ferroelectr. 2007, 89, 12.

- [60] A. K. Tripathi, A. J. J. M. van Breemen, J. Shen, Q. Gao, M. G. Ivan, K. Reimann, E. R. Meinders, G. H. Gelinck, Adv. Mater. 2011, 23, 4146

- [61] J. Lee, A. J. J. M. van Breemen, V. Khikhlovskyi, M. Kemerink, R. A. J. Janssen, G. H. Gelinck, Sci. Rep. 2016, 6, 24407.

- [62] D. Zhao, I. Katsouras, K. Asadi, W. A. Groen, P. W. M. Blom, D. M. de Leeuw, Appl. Phys. Lett. 2016, 108, 232907.

- [63] H. Mulaosmanovic, T. Mikolajick, S. Slesazeck, ACS Appl. Mater. Interfaces 2018, 10, 23997.

- [64] I. Katsouras, D. Zhao, M.-J. Spijkman, M. Li, P. W. M. Blom, D. M. de Leeuw, K. Asadi, Sci. Rep. 2015, 5, 12094.

- [65] R. Xu, S. Liu, S. Saremi, R. Gao, J. J. Wang, Z. Hong, H. Lu, A. Ghosh, S. Pandya, E. Bonturim, Z. H. Chen, L. Q. Chen, A. M. Rappe, L. W. Martin, *Nat. Commun.* 2019, 10, 1282.