### Role of Interface in Ferroelectric Polymer based Memory Diodes

Dissertation

zur Erlangung des Grades

"Doktor

der Naturwissenschaften"

am Fachbereich Physik, Mathematik und Informatik

der Johannes Gutenberg-Universität

in Mainz

Manasvi Kumar

geboren in New Delhi

Mainz, den 11. Mai 2020

1. Gutachter:

2. Gutachter:

Tag der Prüfung: 11.11.2020

### Abstract

Organic electronic devices have the potential to alter our everyday lives with their unique characteristics, such as flexibility, stretchability and low-cost. Among the envisioned devices are non-volatile memories for applications in contactless identification transponders and smart labels. This thesis investigates the operation of such a memory device that uses phase-separated blends of a ferroelectric and semiconducting polymer in a diode configuration. The blend film is composed of columns of semiconductor domains that run continuously through the ferroelectric polymer matrix from the bottom to the top electrode. Polarization of the ferroelectric polymer upon application of appropriate electric fields (greater than coercive field), leads to the modulation of the injection barrier at the metal-semiconductor contact.<sup>28</sup> The diode exhibits a bistable rectifying current-voltage characteristic. Numerical models have been proposed to describe the device physics of the memory diodes.

This thesis provides a potential solution for ambient processing and operation of the memory diodes along with providing the experimental proof of the proposed operation mechanism of the memory diodes. Moreover, current driven memory devices have been demonstrated.

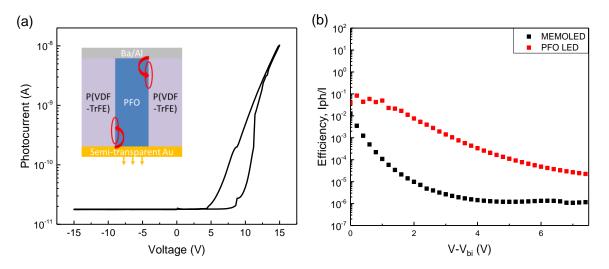

Based on tuneable injection barrier, MEMOLED, a light emitting diode with an inherent ferroelectric switch, has been demonstrated. The advantage of a built-in rectifying switch in the construction of the MEMOLED is to present a non-emissive OFF state and an emissive non-volatile ON state. However, the current efficiency is low as compared to that of pristine semiconductor polymer based OLEDs, and the retention time of the emissive state is short. Here, it is shown that charge trapping in the ferroelectric phase could be a possible reason for the lower performance of the MEMOLEDs. Finally, organic ferroelectric tunnel junctions, based on ultra-thin film of P(VDF-TrFE), with colossal tunneling electroresistance are demonstrated.

## Table of Contents

| Abstract                                                       | iii |

|----------------------------------------------------------------|-----|

| Table of Contents                                              | v   |

| List of Figures                                                | vii |

| Chapter 1                                                      | 1   |

| Introduction                                                   | 1   |

| 1.1 Motivation                                                 | 2   |

| 1.2 P(VDF-TrFE) based memory devices                           | 3   |

| 1.3 Outline of the thesis                                      | 5   |

| Chapter 2                                                      | 7   |

| Theory of Ferroelectric Memory Diodes                          | 7   |

| 2.1 Ferroelectricity                                           |     |

| 2.2 Organic ferroelectric and semiconductor materials          | 11  |

| 2.3 Charge transport in organic semiconductor                  | 15  |

| 2.4 Charge injection                                           | 17  |

| 2.5 Ferroelectric memory devices                               |     |

| 2.6 Charge conduction mechanism in memory diodes               |     |

| Chapter 3                                                      | 25  |

| Interfacial Conduction in Organic Ferroelectric Memory Diodes  | 25  |

| 3.1 Theoretical predictions by numerical models                |     |

| 3.2 The modified memory device structure                       | 27  |

| 3.3 Electrical characterization                                |     |

| 3.4 Numerical simulations                                      |     |

| 3.5 Origin of increase in OFF-state current                    |     |

| 3.6 Conclusion                                                 |     |

| Chapter 4                                                      |     |

| Charge Trapping in MEMOLEDs                                    |     |

| 4.1 The MEMOLED: Memory + OLED                                 |     |

| 4.2 Current efficiency comparison of MEMOLED and PFO based LED |     |

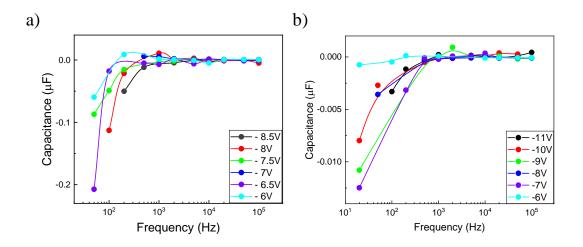

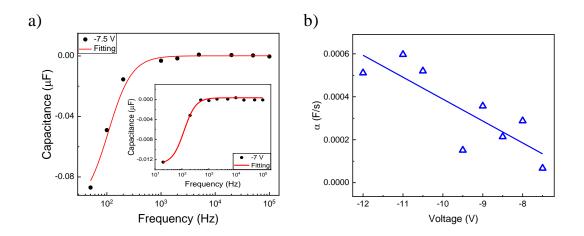

| 4.3 Impedance spectroscopy                                     |     |

| 4.4 Electron trap density analysis                             |     |

|                                                                |     |

| 4.5 Conclusion                                                                        | 41   |

|---------------------------------------------------------------------------------------|------|

| Chapter 5                                                                             | 43   |

| Air-Stable Memory Array of Bistable Rectifying Diodes based on Ferroelectric-         |      |

| Semiconductor Polymer Blends                                                          | 43   |

| 5.1 Processing issues with organic memory diodes                                      | 44   |

| 5.2 Characterization of P(VDF-TrFE):PTAA memory diodes                                | 45   |

| 5.3 Programming of diodes                                                             | 46   |

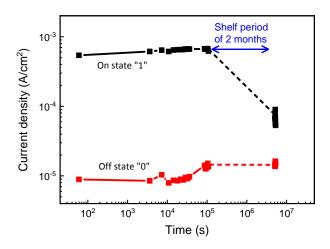

| 5.4 Data retention analysis                                                           | 47   |

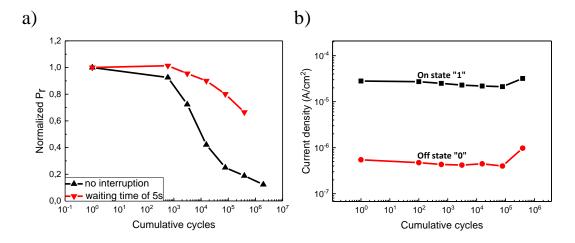

| 5.5 Cycle endurance measurement                                                       | 47   |

| 5.6 Array measurement                                                                 | 48   |

| 5.7 Conclusion                                                                        | 49   |

| Chapter 6                                                                             | 51   |

| Colossal Tunneling Electroresistance in Co-Planar Polymer Ferroelectric Tunnel Juncti | ions |

|                                                                                       | 51   |

| 6.1 Introduction                                                                      | 52   |

| 6.2 Planar FTJs                                                                       | 52   |

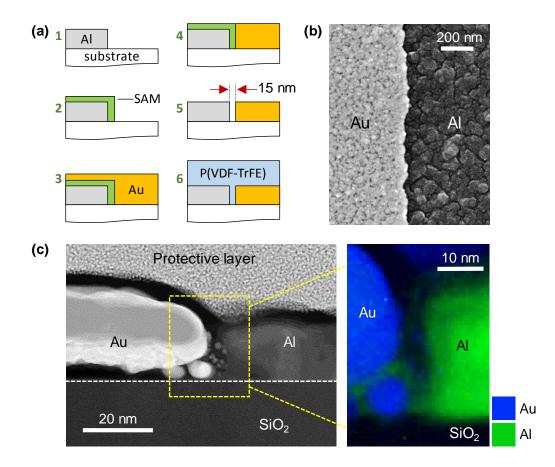

| 6.3 In-plane P(VDF-TrFE) based FTJ fabrication                                        | 54   |

| 6.4 Electrical characterization of FTJ devices                                        | 55   |

| 6.5 Mechanism of charge transport in FTJ                                              | 57   |

| 6.6 Band diagram                                                                      | 60   |

| 6.7 Conclusion                                                                        | 61   |

| Chapter 7                                                                             | 62   |

| Current Driven Ferroelectric Memory Devices                                           | 62   |

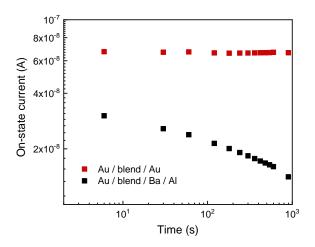

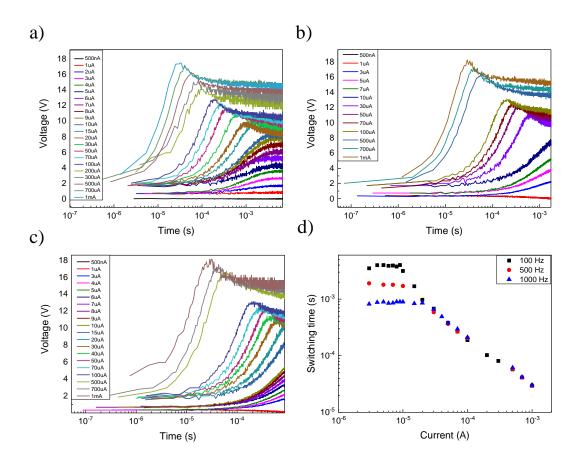

| 7.1 Current induced ferroelectric polarization                                        | 63   |

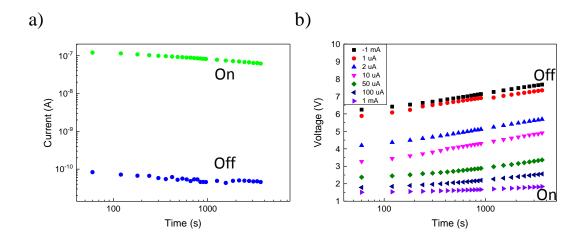

| 7.2 Retention time measurements                                                       | 64   |

| 7.3 Switching time measurements                                                       | 66   |

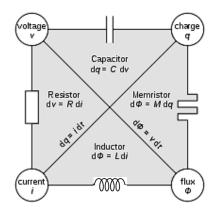

| 7.4 Ferroelectric polymer based memory device – a memristor?                          | 68   |

| 7.5 Conclusion                                                                        | 70   |

| References                                                                            | 71   |

| List of Publications                                                                  | 85   |

| Declaration                                                                           |      |

# List of Figures

| Figure 1. 1. PTAA and P(VDF-TrFE) blend matrix                                                |

|-----------------------------------------------------------------------------------------------|

| Figure 2. 1. Polarization versus Electric field loop for a ferroelectric material             |

| Figure 2. 2. Characteristic form of the <i>C</i> - <i>E</i> curve of a ferroelectric material |

| Figure 2. 3. Schematic illustration of depolarization field, fatigue and imprint 10           |

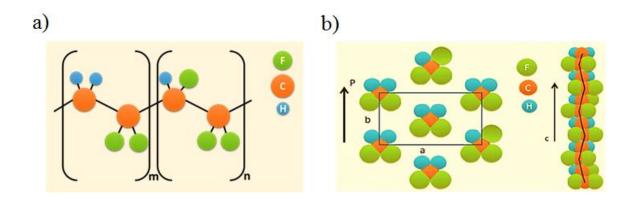

| Figure 2. 4. Chemical formula of P(VDF-TrFE) random copolymer11                               |

| Figure 2. 5. Energy level diagram of an organic semiconductor14                               |

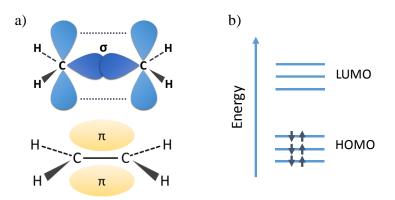

| Figure 2. 6. Schematic showing the formation of Ohmic contact and Schottky contact 17         |

| Figure 2. 7. Electrical characterization of ferroelectric capacitor using Sawyer-Tower 19     |

| Figure 2. 8. Schematic layout of a FeFET                                                      |

| Figure 3. 1. Schematic illustrating charge injection in polymer memory diode                  |

| Figure 3. 2. Schematic describing the modified device structure of the memory diodes 28       |

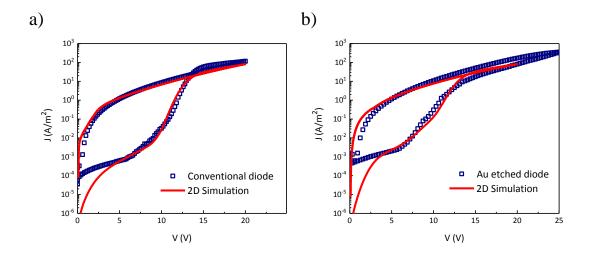

| Figure 3. 3. Current-voltage characteristics of the conventional and modified diode           |

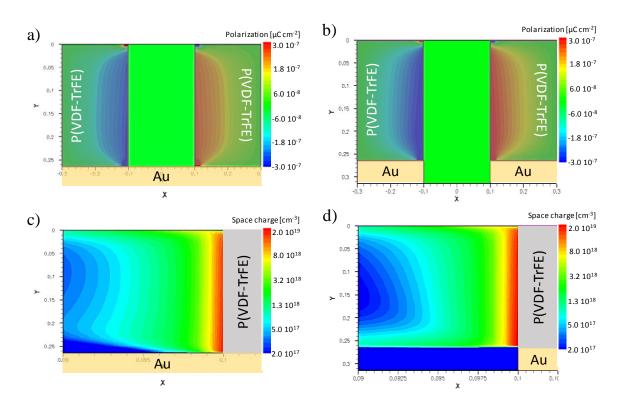

| Figure 3. 4. <i>x</i> -component of the polarization vector in the ON-state                   |

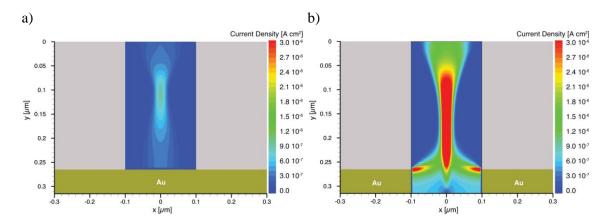

| Figure 3. 5. OFF-state current density calculated with 2D numerical simulations               |

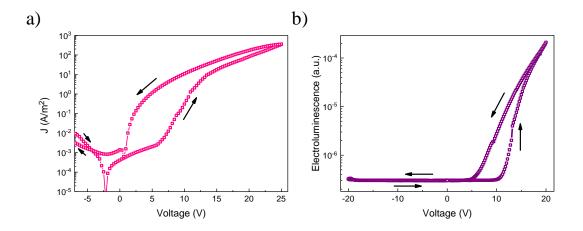

| Figure 4. 1. Current voltage characteristics of a MEMOLED                                     |

| Figure 4. 2. Electroluminescence from a MEMOLED                                               |

| Figure 4. 3. Differential capacitance versus frequency plot with varying voltages             |

| Figure 4. 4. Capacitance versus frequency plot for MEMOLED                                    |

| Figure 4. 5. Illustration of depolarization of P(VDF-TrFE) in diodes                          |

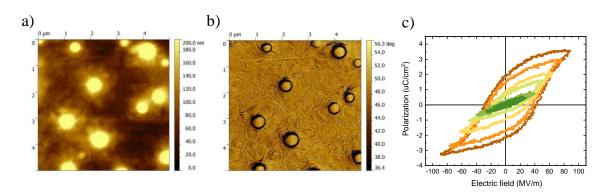

| Figure 5. 1. Surface morphology of the PTAA and P(VDF-TrFE) blend matrix                      |

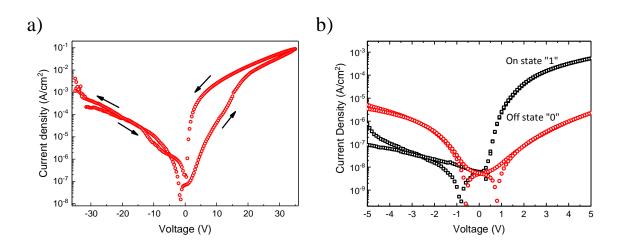

| Figure 5. 2. Full I-V sweep of the PTAA and P(VDF-TrFE) blend memory diode                    |

| Figure 5. 3. Data retention measurement obtained for a diode                                  |

| Figure 5. 4. Fatigue measurements                                                             |

| Figure 5. 5. Schematic and demonstration of cross-bar memory array configured                 |

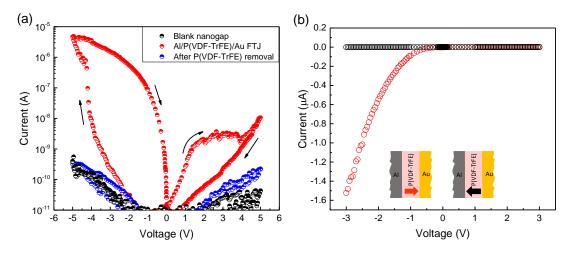

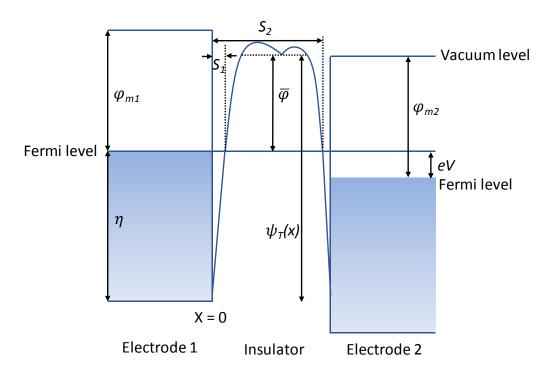

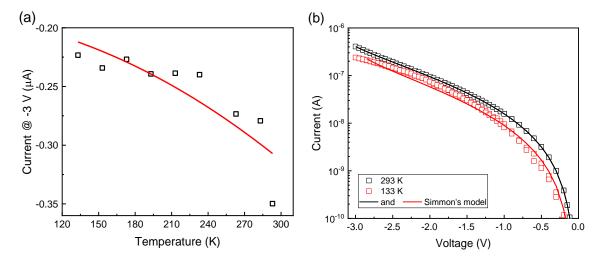

| Figure 6. 2. I-V characteristics of the P(VDF-TrFE) based tunnel junction | . 54 |

|---------------------------------------------------------------------------|------|

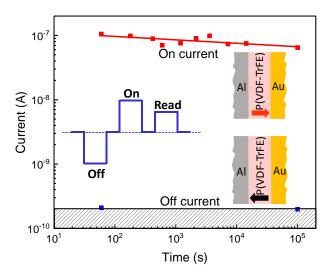

| Figure 6. 3. Retention measurements of both ON- and OFF-states in FTJ     | . 56 |

| Figure 6. 4. Block diagram illustrating Simmon's model                    | . 57 |

| Figure 6. 5. Temperature dependence of the ON-state current               | . 59 |

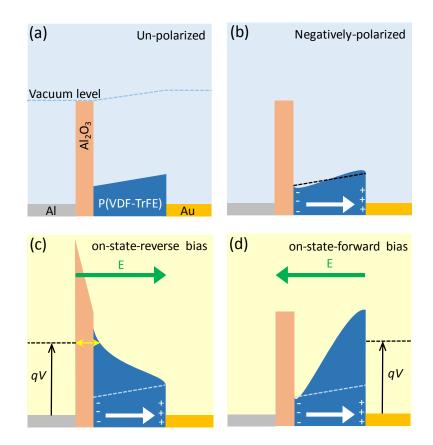

| Figure 6. 6. Tentative energy band diagram of Al/P(VDF-TrFE)/Au FTJ       | . 60 |

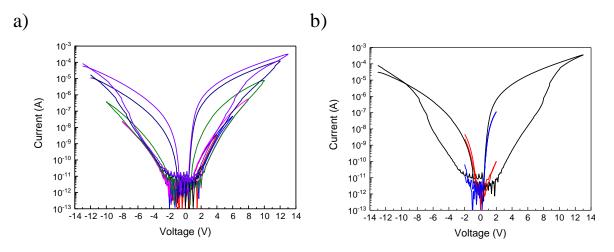

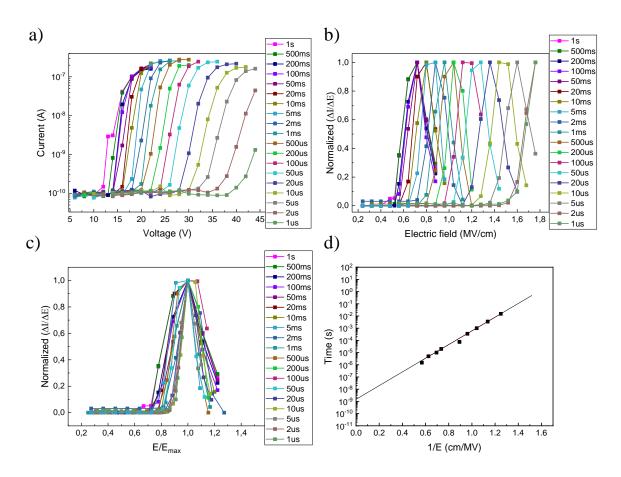

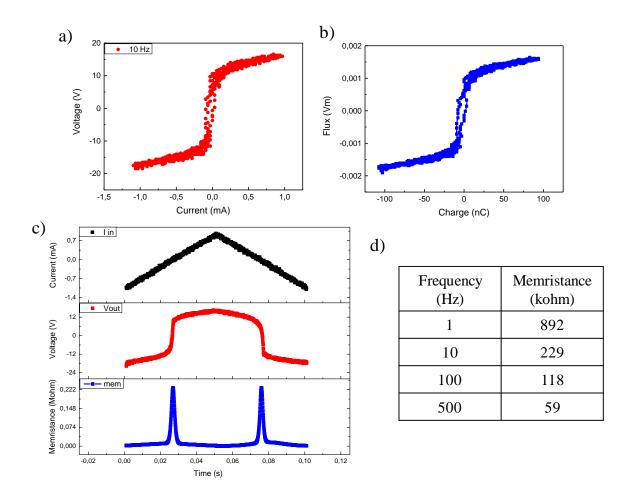

| Figure 7. 1. Hysteretic <i>I-V</i> loops with increasing voltage for a ferroelectric memory device.                        | 53 |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 7. 2. Hysteretic V-I characteristics of the polymer blend memory device                                             | 54 |

| Figure 7. 3. Retention time measurements with current and voltage source                                                   | 54 |

| Figure 7. 4. Switching dynamics of the memory device with voltage pulses                                                   | 55 |

| Figure 7. 5. Switching time measurements with current pulses                                                               | 56 |

| Figure 7. 6. Schematic diagram illustrating qualitative relationships between <i>i</i> , <i>v</i> , $\varphi$ and <i>q</i> | 58 |

| Figure 7. 7. Voltage and Memristance curves corresponding to the current ramp pulse                                        | 59 |

## Chapter 1

### Introduction

An electronic world is what we live in today. The electronic technology positively impacts health, economy and national security. The manufacturing, usage and the disposal of the resources and methodologies needed for these electronic devices, however, negatively impacts the environment. Therefore, an eco-friendlier and cost-effective solution can be offered by the use of organic materials. Moreover, organic materials like polymers and small molecules with unique structures and properties can also offer great potential of novel functionality, competing well with silicon-based devices in flexible applications.<sup>1</sup>

Introduction

#### 1.1 Motivation

Organic materials offer unique characteristics such as flexibility, softness and stretchability, in sharp contrast to inorganic materials such as silicon.<sup>2</sup> Field of applications of organic materials range from flexible displays<sup>3</sup>, artificial skin<sup>4</sup>, information and communication<sup>5</sup>, wearable electronics<sup>6</sup>, to medicine and biomedical research<sup>7</sup>. For example, a major share of the global market of smartphones is occupied by OLED based displays. The new age OLED TVs introduced by Samsung and LG Electronics not only exhibit very high resolution and sharper colour contrast but are also thinner, lighter and much more energy efficient. Organic photovoltaics (OPVs) offer another exciting application of organic electronics.

The most advantageous characteristics of organic materials is solution processing and compatibility with printing and coating techniques, which enables cheap and large-area manufacturing.<sup>8, 9</sup> For example, roll-to-roll manufacturing of solar cell panels would lead to an increase in the throughput at reduced costs. Thus, printed flexible electronics are a part of key future technologies which have the potential to alter our everyday lives.<sup>10, 11</sup>

Memory is a prerequisite for many of the envisioned applications of organic (flexible) electronics such as contactless identification transponders<sup>12, 13</sup> and smart labels<sup>14</sup>. Operation of memory devices make use of the physical property of 'hysteresis' as a result of an applied electric field. The simplest device structures make use of the charging and discharging of capacitors to store information. However, the disadvantage of capacitor technology is leakage of charge, which necessitates restoration of information at regular time intervals.<sup>15</sup> In addition, implementation of such capacitive structures in integrated circuits leads to destructive read-out of the information.<sup>16</sup> This volatility of memory is, in particular, unsuitable for technologies such as RFID (Radio Frequency Identification) tags which use radio frequency for transmission of stored information and, thus, do not have a constant power supply to perform a memory refresh every time.<sup>17</sup>

Finding a non-volatile rewritable memory device is the focus of the active research in the field of memory technology. Some of the many memory technologies being investigated are metal-organic semiconductor-metal junctions<sup>18, 19</sup>, ferroelectricity<sup>15</sup>, charge-trapping effects in field-effect transistors<sup>20-22</sup>, and electro-mechanical switches<sup>23</sup>. Phase-separated blends of ferroelectric and semiconductor polymers have emerged as a potential candidate for realizing memory devices. Poly(vinylidene fluoride co-trifluoroethylene) (P(VDF-TrFE)) is the most common organic material used as the ferroelectric polymer, whereas, various organic

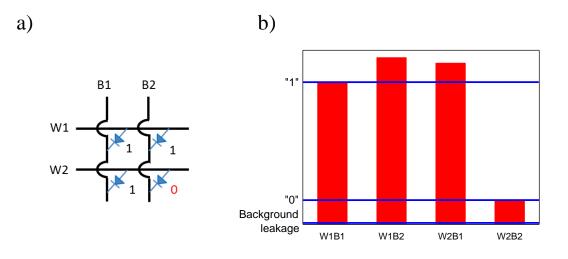

semiconductors ranging from polymers to small molecules have been used as the semiconductor.<sup>24-26</sup> The blend film is sandwiched between two electrodes. The phase-separated morphology is because of spinodal decomposition, wherein columns of semiconductor domains run continuously through the ferroelectric polymer matrix from the bottom to the top electrode.<sup>28</sup> Polarization of the ferroelectric polymer upon application of appropriate electric fields (greater than coercive field), leads to the modulation of the injection barrier at the metal-semiconductor contact.<sup>28</sup> Current densities corresponding to different polarization states ("up" or "down") can be assigned to individual Boolean logic values ("1" or "0"). This information can be then non-destructively read-out at lower voltages (less than coercive field).

#### 1.2 P(VDF-TrFE) based memory devices

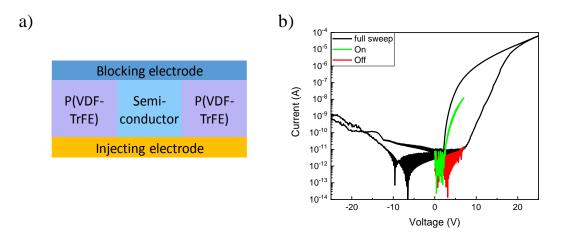

Many solution-processed organic memory devices have been demonstrated so far. The first non-volatile resistive memory with a bistable rectifying current-voltage characteristics was demonstrated by Asadi et al. using phase separated blend films of ferroelectric polymer, P(VDF-TrFE) and semiconductor polymer, rir-P3HT [regio-irregular poly(3-hexylthiophene)]. Polymer blends phase separate due to the low enthalpy of mixing and small entropy gain.<sup>27</sup> The P(VDF-TrFE):rir-P3HT film sandwiched between Ag and LiF/Al electrodes forms the diode device layout. The Ag electrode forms an injection barrier of 0.6-0.7 eV with rir-P3HT HOMO (highest occupied molecular orbital) creating a hole injection limited contact. The LiF/Al contact is a blocking contact for both hole and electron injection. The injection barrier at Ag/rir-P3HT is modulated as the ferroelectric polarizes on application of voltage.<sup>28</sup> Schematic of a typical device structure is shown in Figure 1.1a, along with the *I-V* characteristic illustrating the switching effect shown in the Figure 1.1b. On application of positive bias on the bottom electrode, the ferroelectric is polarized and the charges induced from the metal-semiconductor junction compensates the polarization charges lowering the injection barrier via band bending. This leads to space charge limited charge conduction in the device.<sup>15</sup> On the other hand, in the negative bias, the top contact, being blocking in nature, remains injection limited as the polarization charges are not sufficient to decrease the injection barrier. This results in a rectifying diode. The current remains low (OFF state) at low positive voltages but increases significantly when the coercive voltage of the ferroelectric is reached and the dipoles switch, putting the device in the ON state. This low resistance ON state can be read-out at low voltages (green curve). On applying negative bias, the polarization is switched in the opposite direction and the current remains low because of the injection-limited contact. This is high resistance

Introduction

OFF state and the current remains low when reading at low bias (red curve). These two memory states can be assigned Boolean "1" and "0" and thus, can be read non-destructively.

These memory diodes can be integrated in crossbar array structures. The rectifying nature of the diodes help in reduction of cross-talk between them.<sup>29, 30</sup> Switching time, memory retention and cycle endurance measurements have also been done on these blend devices. The devices have shown a retention time of approximately  $10^6$  seconds. This long retention time results from the stable polarization of the ferroelectric polymer.<sup>31</sup> The switching time of the blend devices is also comparable to that of pristine P(VDF-TrFE) capacitors,  $\approx 10^{-9}$  seconds.<sup>32, 33</sup> In 2011, Asadi *et al.* introduced a concept of MEMOLED as a solution to signage applications with passive addressing.<sup>34</sup> MEMOLED is a light emitting diode with an inherent ferroelectric switch. The study successfully showed MEMOLED as a means of combining active addressing in a passive-matrix crossbar geometry.

**Figure 1. 1.** a) Schematic showing cross-sectional view of the polymer blend memory diodes. Charge is injected into the semiconductor from the injecting electrode. b) Current-voltage (I-V) characteristics of the memory diode. By polarizing the ferroelectric in opposite directions, ON and OFF states can be programmed which can be read at low bias.

Charge transport has also been extensively studied in such organic resistive switches. The proposed charge transport mechanisms include band bending at the semiconductor-metal contact due to polarization<sup>28, 35</sup> and bulk-limited and injection limited conduction in the ON and OFF states respectively.<sup>25</sup> There have been works based on numerical simulations to study the charge transport through the memory diodes, which have shown that interfacial conduction takes place through the devices. Polarization of the ferroelectric leads to stray electric field between the polarization charges and the compensating image charges which lowers the metal-

Introduction

semiconductor barrier.<sup>36, 37</sup> Thus, these ferroelectric polymer based memory diodes have been characterized as interfacial devices, which will be the focus of study in this thesis.

Morphology of the P(VDF-TrFE) blends has also been a subject of extensive research.<sup>38-40</sup> The blend tends to phase separate due to spinodal decomposition and the domains of the semiconductor polymer distribute randomly inside the matrix of the P(VDF-TrFE) after annealing. Several attempts have been made to control this randomness in distribution, namely temperature controlled spin coating<sup>26</sup>, side-chain modification of semiconductor polymer<sup>41</sup> and use of self-assembled monolayer (SAM) to modify the surface energy of the substrate<sup>41</sup>. Patterning and nano-lithography has also been extensively studied to control the interface of the polymer domain structures.<sup>42-45</sup> However, the memory diodes failed to show much improvement apart from a slight increase in the ON state current density. Thus, to this day, random morphology remains the norm of the device fabrication of these memory diodes.

#### 1.3 Outline of the thesis

This thesis focusses on studying the role of interface in the device physics of the memory diodes and novel functionality of the present-day ferroelectric memory diodes. The thesis puts emphasis on the improvement of the memory diodes. *Chapter 2* elaborates the basic theoretical background needed to understand the operation of the ferroelectric polymer based memory diodes. The concept of ferroelectricity, polymer ferroelectrics and semiconductor polymers, as well as charge injection barrier, and transport in the semiconducting polymers are discussed.

*Chapter 3* presents the first experimental proof for the interfacial conduction mechanism in the resistive bistable diodes.<sup>36</sup> *Chapter 4* investigates P(VDF-TrFE)-PFO MEMOLEDs and the effect of electron trap on MEMOLED's operation. *Chapter 5* provides details as how to process and operate the memory diodes in normal ambient conditions and address the issue of air-sensitivity for both fabrication and memory operation.<sup>180</sup>

*Chapter 6* demonstrates ferroelectric tunnel junctions (FTJs) based on a planar electrode configuration, and unambiguously shows that the current transport through a FTJ is dominated by tunneling that is modulated by ferroelectric polarization. Finally, *Chapter 7* discusses current driven ferroelectric memory devices, and shows that the ferroelectric polymer based resistive switches have the potential to be programmed by current pulses as well. The chapter discusses the retention time measurements and switching dynamics of the memory devices by applying

current signals. Furthermore, the potential application of such current driven memory devices in neuromorphic computing has been discussed.<sup>274</sup>

## Chapter 2

### Theory of Ferroelectric Memory Diodes

This chapter elaborates the theoretical background and functioning of ferroelectric polymer based memory diodes. The chapter begins with introducing the basic concepts of ferroelectricity, organic ferroelectric and semiconductor polymer. The concept of injection barrier is discussed in order to understand the charge conduction in the memory devices. Finally, the concept of ferroelectric tunneling is discussed briefly.

#### 2.1 Ferroelectricity

The phenomenon of ferroelectricity was first discovered in 1920 by Valasek in Rochelle salt (KNa(C<sub>4</sub>H<sub>4</sub>O<sub>6</sub>)·4H<sub>2</sub>O), while observing the reversal of polarization upon application of an external electric field.<sup>46, 47</sup> It is analogous to ferromagnetism in iron, showing the property of spontaneous polarization upon cooling below a certain temperature (Curie temperature). In addition, ferroelectric materials (ferroelectrics) exhibit the property of hysteresis between electric polarization and electric field. Therefore, just as the magnetic field B and magnetization M vary with applied magnetizing field H in ferromagnets, dielectric displacement D and polarization P vary with applied electric field E in ferroelectrics. Ferroelectrics also exhibit other phenomena like pyroelectricity (temperature dependent electric polarization of material) and piezoelectricity (electrical polarization due to mechanical stress).<sup>48</sup>

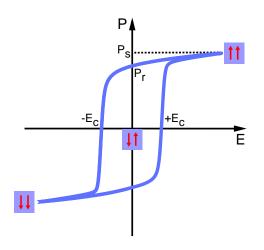

Ferroelectricity remained an interesting, theoretical, phenomenon until 1944, when BaTiO<sub>3</sub> was discovered, which opened the path to ferroelectric memory applications.<sup>48, 49</sup> Soon after the PZT (Pb(Zr,Ti)O<sub>3</sub>) family of materials became the material of choice for FeRAMs (Ferroelectric Random Access Memories). Ferroelectrics have crystalline structures that consist of local polar regions known as domains. Orientation of spontaneous polarization can be different in each domain. At zero electric field these domains are randomly orientated, cancelling each other's polarization and thus, giving zero net polarization at zero electric field. Domain walls are the transition regions between domains of different polarization directions.<sup>50, 51</sup> The characteristic feature of ferroelectric materials is reversal of spontaneous polarization, P upon application of an electric field, E, forcing the dipoles to orient along the direction of the electric field. This leads to a ferroelectric hysteresis loop between P and E (Figure 2.1). The

key features of a ferroelectric are a coercive field,  $E_c$  and remnant polarization  $P_r$ . The  $+E_c$  or  $-E_c$  is the minimum electric field strength required to orient the electric dipoles in either of the "up" or "down" directions, respectively.

$P_s$  is the saturation polarization reached while applying the electric field, i.e., all the dipoles have oriented themselves in the electric field direction. On the other hand,  $P_r$  is the remaining polarization in the material when the electric field is removed. In addition, ferroelectric materials also portray a distinctive feature of phase transition above a certain temperature know as Curie temperature ( $T_c$ ). Above this temperature, ferroelectric phase changes to unpolarized paraelectric phase that is accompanied with structural phase transition.

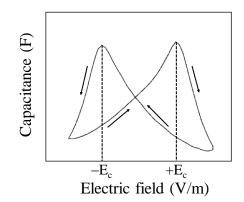

The *P*-*E* hysteresis loop is a necessary but not a sufficient condition to characterize a material as ferroelectric.<sup>52, 53</sup> Phenomenon such as charge trapping-detrapping at Schottky electrodes<sup>54</sup>, leakage current<sup>48</sup> and surface polarization<sup>55</sup> can also lead to hysteresis-like behavior. The ferroelectric nature of a material can also be determined by analyzing its *C*-*V* characteristics. A butterfly-shaped plot of voltage dependence of small signal capacitance is characteristics of a ferroelectric, as shown in the Figure 2.2.<sup>56, 57</sup> The measured response depends upon domain wall motion near the local energy minima along with ionic and electronic displacements. The capacitance peaks at coercive field because of the high concentration of the domain wall at that point.<sup>56</sup>

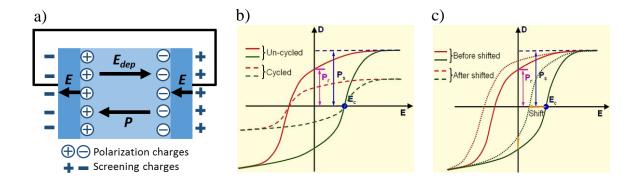

Reliability of a ferroelectric material in memory applications is judged based on three properties, namely, polarization loss, fatigue, and imprint. Retention loss is characterized by the amount of polarization decrease with time as compared to their original state. Depolarization field, along with charge injection and internal built-in voltage, are considered the main causes

**Figure 2. 2.** Characteristic form of the *C*-*E* curve of a ferroelectric material (adapted from reference [93]).

for polarization loss.<sup>58, 59</sup> Depolarization is an inherent phenomenon that arises due to spontaneous polarization. Polarization charges remain uncompensated at the electrode interfaces, giving rise to a depolarization field opposite to the polarization direction, as shown in Figure 2.3a.<sup>60, 61</sup> It is an important issue in ferroelectric devices that can lead to loss of remnant polarization, which increases as the thickness of the ferroelectric material decreases.<sup>62</sup> On the other hand, fatigue is a result of repetitive polarization reversal cycles, leading to reduction in the switchable polarization and shrinking of the *P-E* loop (Figure 2.3b). Thus, fatigue is the measure of loss of polarization charge upon repetitive switching. The cause of fatigue has been attributed to both bulk- and interface-related phenomena. Or more precisely to domain wall pinning by charged defects in both bulk ferroelectric films and at the interface of ferroelectric and electrode.<sup>63-65</sup> Even oxygen vacancies at the interface, which later redistribute themselves within the ferroelectric layer under electrical stress, can lead to reduction in polarization.<sup>66-68</sup>

Lastly, imprint is characterized by the shift of the *P-E* hysteresis loop along the electric field axis and thus, loss of remnant polarization, as shown in Figure 2.3c.<sup>69</sup> Imprint causes, one polarization state to obtain a higher value than the other does. Interpretation of this effect has been based on buildup of an internal bias due to defect in dipole alignment, which again originates from oxygen vacancies.<sup>70, 71</sup> Furthermore, presence of interfacial layer between the ferroelectric and the electrode has also been cited as a cause for imprint.<sup>72, 73</sup>

**Figure 2. 3**. a) Schematic showing the development of screening charges on the metal electrodes on application of electric field, *E* and polarization, *P* in the ferroelectric. Depolarization field,  $E_{dep}$  is formed opposite to polarization direction. Schematics illustrating the phenomenon of b) fatigue and c) imprint. The figures have been adapted from reference [69].

#### 2.2 Organic ferroelectric and semiconductor materials

#### 2.2.1 Organic ferroelectric materials

Current research focusses on many ferroelectric materials, for example, charge transfer complexes, polymers, crystalline organic materials,<sup>74, 75</sup> superamolecular systems, liquid crystallines<sup>76, 77</sup> and hydrogen bonded networks.<sup>78, 79</sup> Although, organic ferroelectrics display inferior performance as compared to their inorganic counterparts, they have shown considerable potential owing to their low temperature processability, substrate flexibility and cost-effectiveness.<sup>80, 81</sup> In this respect, polyvinylidenefluoride (PVDF) and its copolymers with TrFE have been extensively studied. The molecular dipoles along the electropositive hydrogen atoms and electronegative fluorine atoms give rise to polarization which is switchable upon application of an external electric field (Figure 2.4a).<sup>82</sup> Considerable research has been done within the field of PVDF and P(VDF-TrFE) based ferroelectric memory devices<sup>31, 83-87</sup>, along with negative capacitance devices<sup>88</sup>, organic solar cells<sup>89</sup> and multiferroic devices<sup>90</sup>.

Five distinct crystalline forms are exhibited by PVDF polymers, namely,  $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\varepsilon$  and  $\delta$  phases. Formations of each phase uniquely depend on the processing conditions. With the help of poling, stretching and annealing approaches, material can even transit between different phases.<sup>91</sup>  $\beta$  phase exhibits the ferroelectric and piezoelectric phase and has an all-trans (TTTT) zig-zag molecular configuration, with a dipole moment of  $7 \times 10^{-30}$  Cm.<sup>92</sup> The all-trans conformation associated with  $\beta$  phase is enhanced even more upon addition of TrFE monomer to PVDF. This is due to larger steric hindrance induced by fluorine atoms in the overall copolymeric monomer.<sup>82</sup> The schematic of the crystal structure of P(VDF-TrFE) is shown in

Figure 2.4b.<sup>93</sup> The *c*-axis is along the carbon backbone, polarization direction is along *b*-axis and is perpendicular to the *c*-axis, and *a*-axis is perpendicular to the *b*- and *c*-axes. Annealing is performed in order to achieve higher crystallinity of the  $\beta$  phase in P(VDF-TrFE). The most researched composition of P(VDF-TrFE) is 70/30 with the maximum spontaneous polarization value of 10  $\mu$ C/cm<sup>2</sup>.<sup>94</sup> In addition, introduction of TrFE to VDF reduces the phase transition (ferroelectric to paraelectric) temperature or the Curie temperature,  $T_c$  in the copolymer. The greater PVDF content in the copolymer shifts the  $T_c$  to higher temperatures. On increasing the PVDF content from 50 mol% to 80 mol%,  $T_c$  increases from 70 °C to 140 °C. The phase transition  $T_c$  in ferroelectric polymers is of order-disorder type, meaning that the alignment of dipoles becomes randomized and amorphous.<sup>95, 96</sup>

Processing of ferroelectric thin films is relatively easy compared to their inorganic counterparts, due to their simple solution processability. Conventionally, spin coating method has been used to prepare smooth and good quality thin as well as thick films. For PVDF and its copolymers, many solvents are available to choose from, for example, methyethylketone (MEK), dimethylsulphoxide (DMSO), tetrahydrofuran (THF), cyclohexanone, and dimethylformamide (DMF) among others. Film thickness can be controlled by spin parameters like spin speed and acceleration. Homogeneity and roughness depends upon processing conditions like temperature and relative humidity. Favorable conditions for smooth and homogenous thin films are low relative humidity or high substrate temperature.<sup>97</sup> At high relative humidity, the film structure tends to become porous and hence, rough. At high substrate temperatures, however, films are denser and smoother. The morphology of P(VDF-TrFE) thin films, prepared by spin coating, consists of both crystalline and amorphous structures.

Polarization switching in ferroelectric materials has been investigated extensively. The dynamics of ferroelectric switching is quantitatively described by the Kolmogorov, Avrami and Ishibashi (KAI) model.<sup>98-100</sup> The KAI model is based upon an extrinsic switching process of nucleation and domain growth, wherein, the electric dipoles orient themselves in the direction of applied electric field. The process begins with nucleation of domains which grow in longitudinal and transverse directions, and coalesce together resulting in unidirectional dipoles along the electric field.<sup>101</sup>

Time dependent polarization change is given by<sup>102</sup>

$$\frac{\Delta P(t)}{2P_r} = 1 - exp\left(\sum_i \frac{S_i}{S_0}\right)$$

2.1

where,  $S_i$  is the area of growing domains,  $S_0$  is the sample area and  $P_r$  is the remnant polarization at zero electric field. In addition, the KAI model assumes that the growth of a domain, after nucleation, takes place with unrestricted expansion and follows

$$S_i = \left(vt\right)^n \tag{2.2}$$

where, v is the constant domain-wall velocity, t is the time and n is the Avrami index. The normalized change in the polarization can then be written as

$$\frac{\Delta P(t)}{2P_r} = 1 - exp\left(-\left(\frac{t}{t_0}\right)^n\right)$$

2.3

where,  $t_0$  is the characteristic switching time and the Avrami index that depends on the dimensionality of the system of domains. For epitaxial films, n = 2, whereas for single crystals, n = 3.

Merz law defines the relationship between the switching time  $t_0$  and the activation field  $E_a$  as follows<sup>103</sup>

$$t_0 = t_\infty \exp\left(\frac{E_a(t)}{E}\right)$$

2.4

where,  $t_{\infty}$  is the switching time at infinite electric field.  $E_a$  is proportional to domain-wall energy and is inverse functions of temperature. Thus, ferroelectric switches quickly at higher temperatures, requiring less activation field.

Polarization switching in P(VDF-TrFE) has been studied in-depth.<sup>104-107</sup> In thick films, the switching is extrinsic in nature, characterized by nucleation and domain-wall motion. The switching time in P(VDF-TrFE) has been observed to follow Merz law. On the other hand, change in polarization is well described by Eq. 2.3. Extracted Avrami indices have been reported between 1 and 3.<sup>104</sup> The polarization switching depends highly on the microstructure of the polymer film, which in turn depends on the process conditions such as choice of solvent and annealing temperature.

#### 2.2.2 Organic semiconductors

The discovery of chemically doped polyacetylene in 1977 triggered the application of organic conjugated materials as electrically active materials.<sup>108</sup> Apart from flexibility, easy processability and cost effectiveness, there are a number of other advantages of organic polymers in comparison to their inorganic counterparts. Some of them include fine tuning of material properties by molecular restructuring<sup>109</sup>, low temperature processability and large

number of low-cost processing techniques to choose from, for example, spin coating, inkjet coating, bar coating, spray coating, roll-to-roll printing etc.<sup>110-114</sup> Extensive research done in the past two decades, to improve the synthesis and processing of new class of semiconducting polymers, has led to their enhanced performance. This can be seen in applications such as field-effect transistors (OFETs), organic light-emitting diodes (OLEDs) and solar cells.<sup>115, 149, 169</sup>

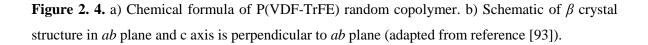

The charge transport phenomenon in inorganic semiconductors is intrinsic in nature, i.e., the thermal agitation leads to excitation of charges from the valence to the conduction band. Typical intrinsic charge densities are in the range of  $10^6$  to  $10^{16}$  cm<sup>-3</sup>, which can be enhanced by doping. Moreover, the atoms are covalently bonded. However, in the case of organic semiconductors, conductivity is extrinsic in nature and is caused by charge injection, from doping or by light induced electron-hole pair generation.<sup>116</sup> Organic semiconductors are class of  $\pi$ -conjugated systems, which are further divided into two categories depending on their weight, namely  $\pi$ -conjugated polymers and small molecules.<sup>117</sup> Molecular structures of both consist of  $p_z$  orbitals of sp<sup>2</sup>-hybridized C atoms forming the conjugated  $\pi$ -electron system. Delocalization of electrons is increased with the  $p_z$ -orbitals participating in the  $\pi$ -bond (Figure 2.5a). The  $\pi$  bonding is significantly weaker as compared to  $\sigma$  bonding, which forms the backbone of the molecules. Thus,  $\pi - \pi^*$  transitions constitute the lowest electronic excitations in conjugated molecules. As shown in Figure 2.5b, the overlapping molecular  $\pi$ -orbitals form the highest occupied molecular orbit (HOMO) in which hole transport takes place. Similarly, electron transport takes place in the overlapping  $\pi^*$  orbitals (anti-bonding), constituting the lowest occupied molecular orbit (LUMO). This corresponds to an energy gap of typically 1.5 to 3 eV, leading to light absorption or emission.<sup>118</sup> The optoelectronic properties can be tuned

**Figure 2. 5.** a) An example of conjugated  $\pi$  electron system in ethane. b) Energy level diagram of an organic semiconductor demonstrating the highest occupied molecular orbitals (HOMO) and the lowest unoccupied molecular orbitals (LUMO).

by varying the factors such as conjugation length and presence of electron donating/withdrawing groups.

#### 2.3 Charge transport in organic semiconductor

Charge transport in organic semiconductor devices is divided into two categories, namely, bulk transport, where the charge carriers are generated within the bulk of the material (e.g., solar cells) or interface transport in which the charge carriers are injected from the metal or oxide electrode into the organic semiconductor material (e.g., organic light emitting diodes and field effect transistors).<sup>115, 119</sup> On the basis of charge transport, organic semiconductor can show electron-only, hole-only or ambipolarity with the ability to transport both electrons and holes.

Charge carrier mobility is the key factor characterizing the charge transport. Charge mobility,  $\mu$  is described by the Einstein-Smoluchowski equation: <sup>149, 169</sup>

$$\mu = \frac{eD}{k_B T}$$

2.5

where, *e* is the electron charge, *D* is the diffusion coefficient,  $k_B$  is the Boltzmann constant and *T* is the temperature. Also, *D* is given by  $\langle x^2 \rangle / nt$ .  $\langle x^2 \rangle$  is the mean square displacement of the charges, *t* is the time and *n* represents dimension of the system. For 1D, 2D or 3D systems, *n* equals 2, 4 or 6 respectively. With application of electric field, mobility is alternatively described as

$$\mu = \nu/E \tag{2.6}$$

where, v is the velocity acquired by the charge carriers in electric field, E.<sup>119, 149, 169</sup>

In a diode configuration, the electrical characteristics are studied by sandwiching an organic film between two electrodes. The electrodes are chosen in a way that only holes or electrons are injected at low voltages. At low voltages the current transport is Ohmic with a slope of 1.<sup>120</sup> The film is thick enough for the charge conduction to be bulk-limited. At higher voltages, the current density, *J* scales quadratically with the applied voltage, *V* and the charge conduction is called space-charge limited current (SCLC). When the number of injected charges is maximized, the built-up electrostatic potential prevents additional charges to be injected and the injection charge density reaches a maximum at the semiconductor-electrode interface.<sup>121, 122</sup>

With the assumption of mobility value to be low and constant, J-V characteristics of SCLC type of conduction is given by the following Mott-Gurney equation<sup>123</sup>

$$J = \frac{9}{8}\epsilon_0\epsilon_r \mu \frac{V^2}{L^3}$$

2.7

where,  $\epsilon_r$  denotes the dielectric constant of the medium and *L* is the material thickness. However, for organic semiconductors, due to their disordered nature, the mobility scales with the width of Gaussian density of states (DOS) ( $\sigma$ ), temperature, electric field and charge carrier density. Disordered nature of the polymers leads to localization of the charge carriers at the molecular bodies like small segments of a polymer chain. Transport of these charge carriers is possible only by hopping to the adjacent sites with variable energies. The hopping sites are often characterized by Gaussian distribution. In addition, the hopping distance statistically varies between adjacent sites. This leads to energetic broadening of the DOS, meaning that the mobility in disordered polymers is several orders lower than in the crystalline counterparts and is temperature and field dependent.<sup>149, 169</sup>

For an electron to hop from  $(r_i, \xi_i)$  to  $(r_i, \xi_j)$ , where *r* and  $\xi$  are the position and energy corresponding to a particular site. In order to hop from site *i* to *j*, it has to overcome a distance of  $R_{ij} = r_j - r_i$  and energy  $\Delta \xi = \xi_j - \xi_i$ . The hopping rate  $\kappa_{ij}$  from site *i* to *j* is described by Miller-Abrahams formalism as follows

$$\kappa_{ij} = \nu \exp(-2\gamma R_{ij}) \exp\left(-\frac{\xi_j - \xi_i}{k_B T}\right) \text{ for } \xi_j > \xi_i$$

2.8

where, *v* denotes the attempt hopping frequency and  $\gamma$  is the overlap factor. It should be noted, that the second exponential becomes 1 for downhill hopping, i.e., for  $\xi_j < \xi_i$ . This formalism is valid for low temperatures and electron-phonon coupling.<sup>119</sup>

Gaussian distribution is attributed to any site in a disordered system. The charge carriers tend to relax into the tail of the Gaussian distribution and the mean energy of them equal –  $\sigma^2/k_BT$ . Mobility scales exponentially with  $1/T^2$  at low carrier densities, and with 1/T at higher.<sup>124</sup> Electric field dependence of mobility follows Poole-Frenkel behavior (E<sup>1/2</sup>) at higher fields, whereas at lower fields, mobility is constant.<sup>125</sup> At higher electric fields, energetic disorder increases as does the diffusion constant and temperature dependence of mobility is also low. At low electric fields, temperature dependence is greater. It is also worth noticing that charge carrier density dependence is dominant over temperature dependence.<sup>126</sup> In addition, morphology of the polymer film has an impact on the mobility. If the film is ordered, then  $\sigma$ will decrease and as a result the mobility increases. For example, in thin film field-effect transistors, mobility is many orders higher due to ordered alignment of the polymer chains.<sup>127,</sup> <sup>128</sup>

#### 2.4 Charge injection

Schottky contact is the interface between the metal and the semiconductor. Barrier height plays a crucial role in determining the current transport to be either space charge limited or injection limited.<sup>129-131</sup>

An Ohmic contact is formed for electrons when the work function of metal,  $\Phi_M <$  electron affinity (EA) or lowest unoccupied molecular orbital (LUMO) of the organic semiconductor. When these two materials are brought into contact, Fermi level ( $\xi_F$ ) aligns with LUMO and flow of electrons takes place. On the other hand, when work function of metal,  $\Phi_M$  > ionization potential (IP) or highest occupied molecular orbital (HOMO), Ohmic contact is formed between the HOMO and metal contact. This causes  $\xi_F$  to align with HOMO, aiding in an uninterrupted flow of holes.<sup>132,133</sup> However, in case the work function lies between IP and EA, such that EA <  $\Phi_M$  < IP, then neither electrons can be transferred from metal to LUMO nor holes from HOMO to the metal. In this case Fermi level pinning does not occur. Moreover, energy barriers are formed for both electron as well as hole injection.

**Figure 2. 6.** a) Schematic of energy level diagram showing the formation of Ohmic contact between a metal and a semiconductor. The dotted lines represent vacuum level, which shift on alignment of the fermi levels. Electron transfer takes place when  $\Phi_M < EA$  (electron affinity of semiconductor), and hole transfer takes place when  $\Phi_M > IP$  (ionization potential of semiconductor). b) Formation of Schottky contact is illustrated in the schematic. When  $\Phi_M > EA$  and  $\Phi_M < IP$ , then a Schottky barrier is formed.

Thermionic injection is the classical model that describes charge injection at Schottky contacts. It is based on charge carriers acquiring enough thermal energy that they are able to overcome the contact barrier. The current density is given by the following expression<sup>134, 135</sup>

$$J = A^* T^2 exp\left(-\frac{\Phi_b - \Delta \Phi}{k_B T}\right)$$

2.9

where,  $A^*$  is the effective Richardson constant,  $A^* = 4\pi q m^* k_B^2 / h^3$ ,  $m^*$  is the effective mass of the charge carrier, h is the Planck's constant and q is the electron's charge.  $\Phi_b$  is the interfacial energy barrier.  $\Delta \Phi$  is the decrease in the energy barrier due to electric field, E and image force effect. Image force effect is the decrease in the potential energy of the injected charge due to the Coulomb interaction between the remaining charges in the metal. The effective barrier is given by<sup>136, 243</sup>

$$\Phi_B = \Phi_b - \Delta \Phi = \Phi_b - \sqrt{\frac{q^3 E}{4\pi\epsilon_0\epsilon_r}}$$

2.10

However, this classical injection model differs for semiconductors with low carriers mobilities. A comparatively low bulk mobility leads to back diffusion of charge carriers. The charge carriers are injected at a high rate from the metal electrode, but due to the low mobility in the bulk of the semiconductor material, they accumulate at the interface and often result in backflow into the electrode.<sup>137</sup> This makes the injection at the interface diffusion-limited, expressed as following<sup>138</sup>

$$J = qN_V\mu E \, exp\left(\frac{-\Phi_B}{k_B T}\right)$$

2.11

with  $N_V$  being the effective density of states.

Another mechanism describing charge injection is field emission or barrier tunneling. It is based on the theory of charge carrier tunneling through the barrier in the presence of an electric field.<sup>139</sup> Fowler-Nordheim model has been used to characterize the quantum mechanical tunneling of the charge carriers through the interface. The current density across the interface is given by

$$J = BE^2 \left(\frac{8\pi (2m^*)^{1/2} \Phi_B^{3/2}}{3hqE}\right)$$

2.12

where, *B* is a constant. For full derivation of the formalism, the reader is suggested to refer to the references<sup>140-142</sup>.

Charge injection by thermionic emission is more relevant to crystalline semiconductors where the energy states are delocalized and charge motion is ballistic in nature. However, in case of organic semiconductors, the energy states are highly localized and charge transport takes place via hopping.<sup>143</sup> In the previous section, the charge transport in an organic semiconductor was described by hopping mechanism between discrete sites by Miller-Abrahams formalism (Eq. 2.8). In order to explain the charge injection through the electrode-semiconductor interface, many models have been demonstrated. Van der Holst came up with a master Pauli equation<sup>144</sup>

$$\sum_{j \neq i, j_x \neq 1, m_x} \left[ W_{ij} p_i \left( 1 - p_j \right) - W_{ji} p_j (1 - p_i) \right] + \sum_{j \neq i, j_x = 1, m_x} \left[ W_{ij} p_i - W_{ji} (1 - p_i) \right] = 0$$

2.13

with the first term describing the hopping between the organic sites. The second term describes the hopping between the electrodes, which are positioned at i = 1 and  $i = m_x$ , where,  $m_x$  denotes the size of the 3D lattice (box). The carrier occupation probability on site *i* is denoted by  $p_i$ . It is assumed that the hopping of charge carriers from one site to another is due to thermally assisted tunneling mechanism. The final injection limited charge density is given by

$$J = J_0 h(E) exp\left(-\frac{\Phi_B}{k_B T} + \left(\frac{1}{2} - c_2\right) \cdot \frac{\sigma^2}{(k_B T)^2}\right) \frac{eaE}{\sigma}$$

$$2.14$$

where,  $J_0 = (ev_0/a^2)exp(-2\alpha a)$  denotes the current density of the system with all the sites fully occupied ( $p_i = 1$ ),  $c_2 = 0.42$  and h(E) describes the field dependence of mobility.<sup>144</sup>

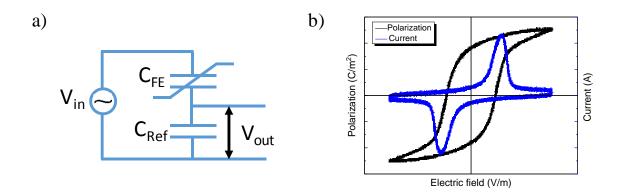

**Figure 2.7.** a) Sawyer Tower circuit diagram used for the electrical characterization of ferroelectric capacitor. b) Polarization vs electric field loop of a P(VDF-TrFE) capacitor (black) and corresponding switching current (blue curve), when the reference capacitor is replaced by a resistor in the Sawyer-Tower.

#### 2.5 Ferroelectric memory devices

Extensive amount of research has been done in the field of memory devices to come up with a viable solution for a wide variety of applications. One of the active domains of this has been ferroelectricity based memory applications, which have shown considerable amount of developments over the past two decades. In this part most common approaches relevant to the scope of this thesis will be discussed.

The simplest of device structures is that of a capacitor. *Ferroelectric capacitors* consist of a film of ferroelectric polymer sandwiched between two electrodes. Sawyer-Tower circuit has been used for electrical characterization of the ferroelectric capacitors, as given in Figure 2.7a. A time varying triangular waveform (frequency 100 Hz) is generated from the function generator (here, Tektronix AFG3102), which is amplified and fed to the ferroelectric capacitive,  $C_{FE}$  device. The applied bias voltage waveform,  $V_{in}$  is fed to channel 1 of the oscilloscope (here, LeCroy Waverunner LT372) as well. The reference capacitor,  $C_{Ref}$  is put in series with the ferroelectric capacitor and the voltage across it,  $V_{out}$ , as a function of time, is measured by channel 2 of the oscilloscope. Upon application of bias, the ferroelectric polarizes causing charges to appear on the capacitor plates to compensate the polarization charges. The amount of charge across the ferroelectric capacitor is same as that of the reference capacitor. By knowing the capacitance value of the reference capacitor, the polarization value can be determined. The applied electric field, *E* is determined by dividing the voltage applied by the thickness, *t* of ferroelectric polymer film. At E = 0, P = D, where, *P* is given by remnant polarization. Thus,  $P \approx D$ , holds as a sufficient approximation and will be used in this thesis.

Memory operation is achieved by applying electric field greater than the coercive field. Correspondingly, the electric dipoles will align in either up or down directions with respect to the field. The *I-V* plot gives characteristic switching peaks at the coercive fields as shown in the Figure 2.7b. A second voltage signal is applied in order to read the programmed state. If the direction of the applied field is the same as the polarization direction then no switching peak will be seen in the *I-V*, as it does not alter the polarization.<sup>15</sup> Thus, the read out of the memory state in a ferroelectric capacitor is destructive in nature, which makes it necessary to reprogram the device after every read operation to its initial memory state after readout. In addition, it costs more power dissipation due to the continuous write-read operations and fatigues the device faster.

Another feature of capacitive structures is that they can be employed in cross-bar arrays, allowing an increase of the memory density on a substrate.<sup>145</sup> Inorganic materials when used in these embedded memory arrays, tend to suffer from "half-select" problem.<sup>67</sup> In brief, to target one memory element, the entire row is supplied with  $(+1/2 V_t)$  and the column with  $(-1/2 V_t)$ . The target element receives  $\pm V_t$  and the state is programmed, while the other elements remain unaffected. This, however, practically is not true. Repetitive application of  $(\pm 1/2 V_t)$  polarizes the neighboring states and results in corruption of data. This problem was rectified by use of active matrix of transistors with "1T 1C" configuration (one transistor for one capacitor). Despite that, it led to cost increase due to additional fabrication steps and larger surface area per element.<sup>146</sup> However, it has been proven experimentally that it is possible to use organic ferroelectric materials (especially P(VDF-TrFE)) in passive geometry without suffering from the "half-select" problem and destructive read out of memory state.<sup>147, 148</sup> This is due to longer switching time of P(VDF-TrFE). This is also optimum enough in order not to disturb the neighboring states and read the desired programmed state at the same time. In addition, the switching time is long enough to read the programmed state and short enough that it does not harm the original polarization of the state, thus, increasing the number of read operations before the need of reprogramming arises.

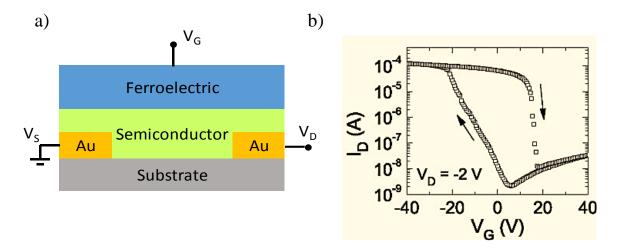

Another class of memory devices is *ferroelectric field-effect transistors* (FeFET) with a ferroelectric material constituting the gate dielectric. The FeFETs operate based on the resistive switching induced by polarization of the ferroelectric gate dielectric. Structural layout of FeFET comprises of a stack of metal-semiconductor-ferroelectric materials, with the ferroelectric layer

**Figure 2. 8.** a) Schematic layout of a FeFET with Au as source drain electrodes. b) *I-V* transfer curve of a *p*-type FeFET, with arrows indicating the sweep direction (adapted from reference [149]).

serving as the gate dielectric. Depending on the polarization orientation of the ferroelectric, charges are induced through the ferroelectric-semiconductor interface into the semiconductor channel. The ferroelectric polarization changes depending on the gate bias, which shifts the injected charge density in the semiconductor, which further defines the drain current levels. The high and low drain current levels can be correspondingly defined as Boolean "1" and "0".<sup>15, 149</sup> The high and low semiconductor channel conductance is maintained even after the gate voltage is removed, making the read-out non-destructive.<sup>15</sup> It has been seen that the ON state of the FeFET is stable due to the polarized state of the ferroelectric gate; however, the OFF state is not thermodynamically stable. The lack of compensation charges from the semiconductor leads to an increased depolarization field in the device.<sup>15, 150</sup> As an example, *I-V* characteristic of a typical *p*-type unipolar FeFET is demonstrated in Figure 2.8b. The current remains low at the beginning of the curve, as the ferroelectric remains unpolarized. At switch-on voltage, the current starts to increase with increase in the negative bias and saturates when the negative coercive voltage (~ -20 V) is reached, as the ferroelectric becomes fully polarized. This is the ON state. Upon back scanning, the ferroelectric remains polarized and the current remains high. At around +20 V, the ferroelectric polarization switches and the current decreases as the electrons cannot be injected into the *p*-type semiconductor. This puts the device in OFF state.<sup>149</sup> The main figure of merit of an organic FET (OFET) device is the field-effect mobility, whose value has changed drastically from ~  $10^{-6}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> to nearly 10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.<sup>151-155</sup> Temperature independent charge transport with high mobility has been observed in highly ordered semiconductor materials like pentacene and heteroacene derivatives.<sup>155-157</sup> Semicrystalline materials such as conjugated polymers P3HT and PBTT have also been the focus of research.151, 158-160

The destructive nature of information read out can also be avoided by the use of a diode structure, which was discussed in detail in the previous chapter. The current rectifying property of the ferroelectric diodes also help in minimizing the "cross-talk" phenomenon, which can occur in integrated memory arrays.

#### 2.6 Charge conduction mechanism in memory diodes

2D numerical models have been proposed explaining the device physics behind the operation of ferroelectric diodes. In this section, the operation mechanism will be discussed. The development of a stray electric field between the compensating image charges and the polarization charges inside the polarized ferroelectric leads to barrier lowering.<sup>161</sup> Along with

the stray electric field inside the device, tunneling of charge carriers through the metalsemiconductor interface and accumulation at the semiconductor side also takes place.<sup>37</sup> 2D polarization of the ferroelectric phase leads to the bending of electric field lines near the semiconductor phase. This results in charge conduction along the interface of the P(VDF-TrFE) and the semiconductor phase.<sup>36</sup> The numerical model also considered variable range hopping theory for charge conduction in the organic semiconductor,<sup>162</sup> along with disorder<sup>163-165</sup>. Physical equations solved in the numerical simulator included continuity, Poisson and driftdiffusion transport equations.<sup>166-169</sup> The charge flow at the ferroelectric-semiconductor interface was defined together with thermionic emission, energy disorder, drift-diffusion, tunneling and barrier lowering by image force.<sup>37, 138, 144, 170-172</sup>

However, most importantly ferroelectric polarization was considered as a function of electric field.<sup>168, 173, 174</sup> The ferroelectric polarization was modelled following the approach of Miller *et al.*<sup>174</sup> The model is described as following

$$P_s(E) = P_{sat} \cdot \tanh\left(\frac{E - E_c}{2.E \cdot \left(ln\left(\frac{1 + P_r / P_{sat}}{1 - P_r / P_{sat}}\right)\right)}\right)$$

2.15

where,  $P_s$  is spontaneous polarization,  $P_{sat}$  is saturation polarization, and  $E_c$  is coercive field.

To model the charge transport in semiconductor, hole only device with PFO as semiconductor was fabricated with electrodes that form Ohmic contact with PFO. Polymer semiconductors like PFO are typically disordered, thus, they are characterized by localized states. The charge conduction in disordered semiconductors is via thermally activated hopping as described in section 2.3. The hopping rate between donor and acceptor sites is given by Eq. 2.8. The macroscopic conductivity,  $\Gamma$  is given by the following equation<sup>37, 162, 163, 175</sup>

$$\Gamma = \Gamma_0 \exp\left(\frac{\xi_F}{k_B T}\right)$$

2.16

where,  $\Gamma_0$  is proportional to *T*,  $\sigma$ ,  $v_0$  and inter-site distance. The drift-diffusion equation for hole transport inside the semiconductor is given by the following

$$\vec{J}_p = \Gamma \nabla \varphi + q D_p \nabla_p \tag{2.17}$$

where,  $J_p$  represents hole current density,  $\varphi$  is the electric potential and  $D_p$  is the hole diffusion constant. The continuity equation is described by

$$\frac{dp}{dt} = -\frac{1}{q} \, \nabla. \vec{J}_p \tag{2.18}$$

and the Poisson equation by

$$\rho = \epsilon_0 \epsilon_r \nabla. \vec{E}$$

2.19

where,  $\rho$  is the net charge carrier concentration and  $\vec{E}$  is the electric field.

The charge injection mechanism is described by thermionic emission and barrier tunneling for crystalline inorganic materials. However, for disordered semiconductors, charge hopping mechanism has been proposed for charge injection as shown in the section 2.3. The barrier lowering due to image forces has been previously discussed and is given by Eq. 2.10. The effective hole charge carrier density at the interface of electrode and the semiconductor, due to effective energy barrier,  $\Phi_b$  is approximated to <sup>37</sup>

$$p_0 = N_t exp\left(\frac{-1}{k_B T} \times \left(\Phi_b - \sigma^2 / 2k_B T\right)\right)$$

2.20

Other charge injection mechanisms include thermionic emission given by the following equation

$$J_p = \frac{AT^2}{N_t} (p - p_0)$$

2.11

with *A* as the Richardson constant. Barrier tunneling describes the hole carrier density flowing through the metal-semiconductor interface as

$$J_{tun} = \frac{AT}{k_B T} \int_{-\infty}^{+\infty} \kappa_p(r,\xi) \times \psi(r,\xi) \,\partial\xi$$

2.12

Here,  $\kappa_p(r,\xi)$  is the tunneling probability given by Wentzel-Kramers-Brillouin (WKB) approximation<sup>176</sup> and  $\psi(r,\xi)$  is a logarithmic function of position-dependent Fermi energy,  $\xi_F(r, )$ . The reader is suggested to refer to the reference<sup>37</sup> for details of the model and parameters used.

Thermionic emission and charge tunneling mechanisms explain the charge transport in crystalline (ordered) semiconductors where the charge conduction is governed by band-like transport. However, organic semiconductors have amorphous structures, which make charge hopping the major charge transport mechanism in them. So far, basic components of charge transport in semiconductor, P(VDF-TrFE) and at the interface of the metal-semiconductor have been described in brief.

## Chapter 3

### Interfacial Conduction in Organic Ferroelectric Memory Diodes

This chapter presents the experimental proof of interfacial charge conduction in memory diodes based on phase-separated blends of ferroelectric and semiconducting polymers. To do so, in the diode structure the electrode contacting the semiconductor phase has been intentionally modified.\*

\*The results presented in this chapter have been published in H. Sharifi Dehsari, M. Kumar, M. Ghittorelli, G. Glasser, T. Lenz, D. M. de Leeuw, F. Torricelli and K. Asadi, *Applied Physics Letters* 113, 093302 (2018).<sup>36</sup>

#### 3.1 Theoretical predictions by numerical models

Solution processed blend of a ferroelectric and a semiconductor polymer undergoes spinodal decomposition phase separation yielding a thin-film with bicontinuous columnar semiconducting domains that are randomly distributed in the P(VDF-TrFE) matrix.<sup>38, 40, 177, 178</sup> To realize a bistable rectifying diode, the injecting electrode is chosen such that it forms a Schottky contact with a large barrier height with the semiconductor. The ferroelectric polarization modulates the injection barrier, enabling reversible switching of the diode resistance between a high-resistance OFF-state and a low-resistance ON-state.<sup>25, 37</sup>

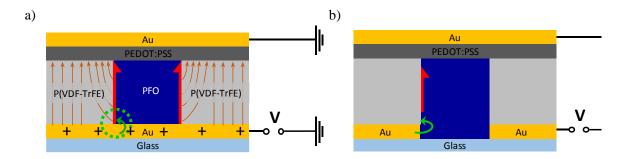

Charge conduction in these memory devices has been extensively investigated. Twodimensional (2D) numerical models have been presented describing the *I-V* characteristics on the basis of ferroelectric polarization and charge injection through metal-semiconductor interface.<sup>25, 37, 168, 174</sup> The model predicts bending of the electric field lines near the semiconductor phase, due to the emergence of an in-plane component for the ferroelectric polarization, as shown in Figure 3.1a. As a result, a large stray electric field exists at the semiconductor-P(VDF-TrFE) interface. The bottom contact facilitates tunneling of the charge carriers and effectively lowers the barrier for charge injection. Appearance of the *x*-component of the electric field leads to confining of the injected charge carriers in the semiconductor to the interface with P(VDF-TrFE) phase, as illustrated by the red arrows in Figure 3.1a. The 2D simulations thus predict that the memory diode is an interface device, wherein the charge injection occurs only through the fraction of the contact just underneath the

**Figure 3. 1.** Schematic illustrating a) Structure of conventional memory diode. Electric field distribution in the P(VDF-TrFE) phase is shown by orange arrows. The thick red-arrows show confinement of the current to the PFO phase boundaries. b) Bottom-contact-etched memory device structures. The green-arrows show that charge injection takes place at the corner of the ternary interface (between the injecting contact with the PFO|P(VDF-TrFE)). Both diode structures should give the same switching behavior.

semiconductor|P(VDF-TrFE) interface, as shown in Figure 3.1a. Therefore, only the corner point of contact is needed for the memory operation and the charge conduction inside the device takes place along the semiconductor|P(VDF-TrFE) interface. However, to back these key theoretical findings, no experimental proof has been given so far.

Thus, in this chapter, we unambiguously demonstrate charge injection from the contact point just beneath the semiconductor|P(VDF-TrFE) interface in the memory diodes. To this aim, a new memory device structure, shown in Figure 3.1b, was realized. The part of the injecting bottom electrode in contact with the semiconductor is removed, leaving only the contact point under the semiconductor|P(VDF-TrFE) interface for charge injection to take place. Poly(9,9-dioctylfluorene) (PFO) was used as the semiconductor polymer. It is experimentally demonstrated that the memory diode shows a similar on-current upon switching of the ferroelectric polymer, while the off-current shows subtle but relevant differences. Furthermore, 2D numerical simulations were performed taking the specific diode geometry into account. It was seen that the model successfully reproduced the experimentally measured *I-V* characteristics with an identical set of parameters for both diode geometries and further explained the origin of the observed OFF-state current. Moreover, the findings of this work can be employed for further optimization of the memory devices, and light-emitting diodes with built-in ferroelectric memory functionality e.g. the MEMOLEDs.<sup>34, 179</sup>

#### 3.2 The modified memory device structure

Poly(vinylidene fluoride-trifluoroethylene) (PVDF-TrFE) with the composition of 65%–35% was used as the ferroelectric polymer in this work. It was purchased from Solvay, Belgium. Poly(9,9-dioctylfluorene) (PFO) was used as the semiconductor polymer and was purchased from TNO, The Netherlands. All polymers were used as received. Cyclohexanone, was used as the common solvent and was purchased from Sigma Aldrich. Top polymer electrode, PEDOT:PSS (CLEVIOS P VP AI 4083) was purchased from Heraeus. All chemicals and polymers were used as received without further purification.

Conventional memory diodes, as shown in Figure 3.1a with Au (50 nm)/PFO:P(VDF-TrFE) (270  $\pm$  10 nm)/PEDOT:PSS (70 nm)/Au (70 nm), were prepared from a solution of 4 wt. % PFO:P(VDF-TrFE) in cyclohexanone with a polymer weight ratio of 1:9. Both polymers were dissolved in a common solvent and the solution temperature was kept at 80 °C for about 1 hour.<sup>180</sup> The blend solution was filtrated using 1 µm polytetrafluoroethylene (PTFE) filters prior to film deposition. Next, the substrates were annealed in a vacuum oven (10<sup>-1</sup> mbar) at 140 °C

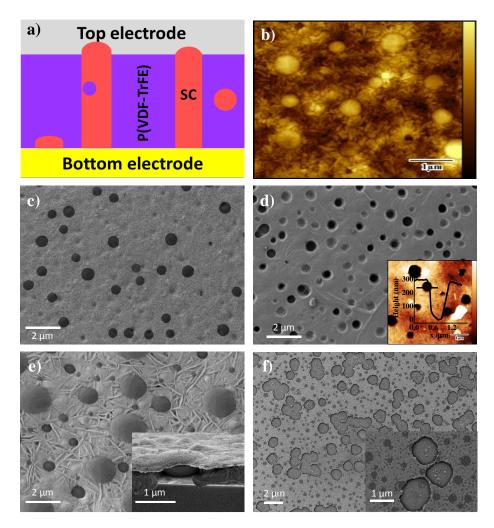

for 2 hours to enhance the crystallinity of the P(VDF-TrFE) phase. Wire-bar coating technique was used for preparing polymer blend thin films for organic ferroelectric memory diodes. The instrument used was K202 control coater (RK PrintCoat Instruments Ltd, UK). The desired phase-separated morphology of the polymer blend films P(VDF-TrFE)/PFO was realized by controlling the glass substrate temperature. By the precise control of the substrate temperature, high quality thin films with low roughness were obtained. Polymer blend films of ~250 nm thickness were prepared. Devices were finished by deposition of top electrodes.<sup>36</sup> The final

**Figure 3. 2.** a) Schematic illustrating the final device structure of the conventional memory diodes based on ferroelectric-semiconductor polymer blend. b) AFM and c) SEM images showing the phase separated morphology of PFO:P(VDF-TrFE) polymer blend. d) SEM and AFM topography images of the films after PFO removal. The height profile of the AFM image is from 0 to 300 nm (excluding the bright area which corresponds to dust). The line profile shows PFO domains are fully etched away. e) Top view SEM images of a PFO back-filled film after annealing (inset showing cross-sectional SEM image). f) SEM image of an etched Au electrode.

device layout is given in Figure 3.2a. Cr/Au was used as the bottom electrode in the fabrication of polymer blend memory diodes, with Cr acting as an adhesive between the glass substrate and the Au bottom electrode. Atmospheric thin-film processing of P(VDF-TrFE) leads to very rough films, due to vapor induced phase separation (VIPS).<sup>38, 181</sup> Increasing the substrate temperature suppresses VIPS and thereby allows for realization of ultra-smooth P(VDF-TrFE) thin-films suitable for microelectronic applications. Hence, to prevent VIPS and roughening of the surface, the substrate temperature is set at 70 °C. Formation of a phase separated microstructure, wherein the semiconductor polymer domains are continuous through the film thickness, is crucial for the operation of the diode. The bright circular domains are in the amorphous semiconductor phase. The surrounding matrix is P(VDF-TrFE) with a distinct needle-like microstructure.

For obtaining the device structure of diodes in Figure 3.1b, the following was done: after deposition of the PFO:P(VDF-TrFE) blend film, in order to realize a self-aligned etching mask for the gold bottom electrode, PFO domains were selectively etched away using an orthogonal solvent, e.g. hot toluene (60 °C) overnight.<sup>177</sup> Afterwards, the substrates were blow dried with nitrogen, following which, they were immersed in a diluted solution of KI:I<sub>2</sub>:H<sub>2</sub>O (0.1:0.016 M or 0.05:0.008:27 mol ratio). To prevent severe gold under etching, the etching time was optimized to about 3 minutes. After the etching process, the substrates were thoroughly washed with DI-water and dried in vacuum oven at 80 °C for 2 hours. Subsequently, the holes in the P(VDF-TrFE) layer were back filled with pure PFO using spin coating. Pure PFO was prepared from a 0.5 wt% solution in toluene. After the PFO back-filling the films were annealed at 140 °C for 2 hours. There was no apparent formation of a PFO ad-layer.<sup>37, 168</sup> It should be noted that the memory diodes also operate if an ad-layer is present provided that its thickness is below 70 nm.<sup>35</sup> The devices were finished with deposition of the top electrodes.

For morphological analysis, SEM (using Zeiss 1530 Gemini) and AFM (using Nanoscope Dimension 3100) scanning was done at every step of device fabrication. Figures 3.2b and,-c show the top view AFM and SEM micrograph of the blend thin-film. The micrographs show typical morphology of the phase-separated PFO:P(VDF-TrFE). The average diameter size of the PFO domains amounted to 300-500 nm. The selective removal of the PFO domains is captured in the SEM image shown in Figure 3.2d. The inset shows the AFM height profile of the film. It can be seen that holes extend through the whole film thickness reaching the bottom contact.

The next steps of the bottom Au electrode etching, back-filling with PFO, and subsequent annealing at 140 °C is showing in Figure 3.2e. The inset provides the cross-sectional SEM image, showing a complete back-filling of the holes. It can be seen that the backfilled PFO domains in Figure 3.2e are larger than the PFO domains in Figure 3.2c because an excess amount of PFO was used for the backfilled case, resulting in overfilled domains. Besides, this overfill has no influence on the switching of the injection barrier since the experiments were done at the bottom contact. To evaluate the morphology of the Au bottom electrode, P(VDF-TrFE) masking layer was removed after the Au etching process by immersing the substrate in cyclohexanone overnight. The result is shown in Figure 3.2f, showing the SEM image of the etched Au bottom contact. Round holes are formed in the Au bottom electrode, exposing the glass substrate underneath. However, the size of the etched regions are slightly larger than the size of the removed PFO columns, which could be because of slight over etching of gold.

#### 3.3 Electrical characterization

To investigate the working of the modified memory diodes, electrical measurements were carried out. For *I-V* measurements, Keithley 4200 SCS and 4155B Semiconductor Parameter Analyzer from Hewlett Packard was used. The device under test was kept in a probe station and bias was applied on the bottom electrode in all the measurements. The devices were kept under vacuum ~  $10^{-5}$  mbar. A voltage sweep from 0 V to +20 V and back from +20 V to 0 V was

**Figure 3. 3.** Current-voltage characteristics of a a) conventional diode with device layout as shown in Figure 3.1a, and b) of a diode with etched gold bottom electrode, with a device layout as shown in Figure 3.1b. The solid lines are the results of the numerical 2D simulations.

applied to the bottom Au electrode, while keeping the top electrode grounded. For reference, *I*-*V* sweep characteristics of a conventional diode are shown in Figure 3.3a. In brief, the current density is low at low bias, since Au-PFO contact is injection limited. The device remains in the high resistance OFF-state. With increase in bias, P(VDF-TrFE) polarizes, increasing the current through the device, and the resistance is lowered by several orders of magnitude, putting the device in the ON-state. Upon sweeping back, the ferroelectric polarization is maintained, and the diode remains in the ON-state. The diode is put back into the OFF-state on application of a bias larger than the negative coercive voltage.

Interestingly, the Au-etched device demonstrated similar hysteretic *I-V* characteristics, as shown in Figure 3.3b. The ON-state current is almost the same as that of the conventional diode. However, the OFF current is marginally higher. Origin of this divergence will be discussed later in this chapter. Presentation of hysteretic *I-V* characteristics for the diode with modified contact is a conclusive proof of the ferroelectric memory diodes being interface devices, exhibiting charge injection through ferroelectric|semiconductor interface.

**Figure 3. 4** *x*-component of the polarization vector in the ON-state for the device in a) conventional memory diode and b) Au-etched diode geometry. Hole density distribution in the PFO pillar in the ON-state for the device with c) conventional geometry and d) Au-etched diode geometry.

#### 3.4 Numerical simulations

2D simulations were performed in order to support the above-mentioned experiment, focusing particularly on the point of contact between the injecting electrode and ferroelectric|semiconductor interface. In the model developed by M. Ghittorelli et al., behavior of ferroelectric polarization with applied bias and charge conduction through the semiconductor phase is considered.<sup>37, 138, 144, 162-165, 170, 172, 182, 183</sup> The details of the model has been previously discussed in Chapter 2. Solid lines in the Figures 3.3a and, -b represent the simulation using the model, for conventional and Au-etched memory diodes, respectively. Parameters such as mobility and hopping distance were kept identical for both devices. For PFO, the average intersite distance,  $d_a = 1.5$  nm and the energy disorder parameter,  $\sigma = 0.16$  eV. The HOMO level of PFO was taken to be 5.8 eV and the work function of Au, measured by Kelvin probe, amounted to 4.5 eV - 4.6 eV, resulting in an injection barrier of ~1.3 eV. The simulations reproduce the full hysteretic I-V characteristics.