# Observation of Optically Addressable Nonvolatile Memory in VO<sub>2</sub> at Room Temperature

Youngho Jung,\* Junho Jeong, Zhongnan Qu, Bin Cui, Ankita Khanda, Stuart S. P. Parkin, and Joyce K. S. Poon

Vanadium dioxide (VO<sub>2</sub>) is a phase change material that can reversibly change between high and low resistivity states through electronic and structural phase transitions. Thus far, VO<sub>2</sub> memory devices have essentially been volatile at room temperature, and nonvolatile memory has required non-ambient surroundings (e.g., elevated temperatures, electrolytes) and long write times. For the first time, here, the authors report the observation of optically addressable nonvolatile memory in VO<sub>2</sub> at room temperature with a readout by voltage oscillations. The read and write times have to be kept shorter than about 150  $\mu s$ . The writing of the memory and onset of the voltage oscillations have a minimum optical power threshold. Although the physical mechanisms underlying this memory effect require further investigations, this discovery illustrates the potential of VO<sub>2</sub> for new computing devices and architectures, such as artificial neurons and oscillatory neural networks.

#### 1. Introduction

Phase-change materials (PCMs) are important candidates for next generation computing devices and systems, including artificial neurons and neuromorphic computing that aim to improve power consumption and speed in data transfer.<sup>[1-10]</sup> A PCM gaining much interest for such applications is the transition metal oxide, vanadium dioxide (VO<sub>2</sub>), which can reversibly change between its insulator and metal states by thermal,<sup>[11]</sup> electrical,<sup>[12,13]</sup> optical,<sup>[14]</sup> or mechanical stimuli<sup>[15]</sup> or by ionic liquid gating.<sup>[16-18]</sup> The phase transition has an hysteresis that

Dr. Y. Jung, Dr. J. Jeong, Dr. B. Cui, Prof. S. S. P. Parkin, Prof. J. K. S. Poon Max Planck Institute of Microstructure Physics Weinberg 2, Halle 06120, Germany

E-mail: youngho.jung@mpi-halle.mpg.de

Dr. Y. Jung, Dr. J. Jeong, Z. Qu, A. Khanda, Prof. J. K. S. Poon

Department of Electrical and Computer Engineering University of Toronto

10 King's College Rd., Toronto, Ontario M5S 3G4, Canada

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aelm.202001142.

© 2021 The Authors. Advanced Electronic Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

DOI: 10.1002/aelm.202001142

is utilized for memory  $^{[15-17,19-21]}$  and the negative differential resistance (NDR) regime of the VO<sub>2</sub> leads to voltage or current oscillations.  $^{[12,22-24]}$

Thus far, the VO2 insulator-metal transition (IMT) due to a structural phase transition (SPT) has been volatile at room temperature, making a VO<sub>2</sub> memory cell power-inefficient. Nonvolatile phasechange has been observed in VO2 on a piezoelectric substrate, but the nonvolatility is due to remnant strains in the piezoelectric material rather than the VO<sub>2</sub> itself.[15] Tuning the oxygen vacancy concentration using a gated electrolyte<sup>[16]</sup> or hydrogenation<sup>[17]</sup> of VO<sub>2</sub> can lead to nonvolatile, reversible phase transitions but, to date, it is very slow (requiring minutes and up to hours) as summarized in Table S1, Supporting Information.

Other observations of nonvolatile  $VO_2$  memories required an external bias, in the form of a raised temperature or applied voltage, to maintain their memory states. [19–21] Here, we report the observation of nonvolatile  $VO_2$  memory at room temperature with sub-millisecond writing and reading times. The nonvolatile memory state is accessed within the narrow hysteresis of the first major transition in current-biased  $VO_2$ ; it persists in the ambient environment without the application of an external bias or excitation. Interestingly, compared to typical nonvolatile memory, where the readout is measured by two or more distinct physical states, our written memory is read out as voltage oscillations between the insulator and metal states.

#### 2. Results

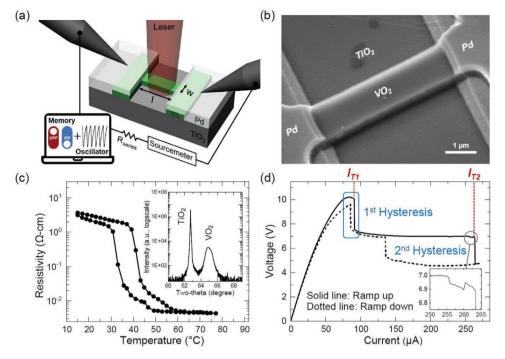

Before discussing the details of the experiments, we first provide an overview of the device operation and the observed phenomenon. The device consisted of two electrical terminals patterned on an etched VO<sub>2</sub> microwire (**Figure 1a**). A typical VO<sub>2</sub> microwire exhibits a voltage-current (VI) relation as shown in Figure 1d, which consists of two major transitions at  $I_{T1}$  and  $I_{T2}$ , between which is a NDR region. It is often believed that  $I_{T1}$  corresponds to a mostly carrier-induced onset of the IMT, whereas  $I_{T2}$  corresponds to a largely thermally-driven Peierls SPT transition. [13,25,26] Smaller step transitions can also often be observed at currents near  $I_{T2}$  in thicker (~30 nm or more) films of VO<sub>2</sub> on TiO<sub>2</sub> due to nanoscale line cracks, [27] but they do not

**Figure 1.** a) 3D schematic of the device and experimental setup. b) A scanning electron micrograph of a representative  $VO_2$  microwire with palladium (Pd) contacts. c) Measured resistance of a  $VO_2$  device as a function of stage temperature. Inset, X-ray diffraction (XRD) spectrum of a  $VO_2$  film on a  $TiO_2$  (001) substrate. d) Typical example of VI measurement at room temperature, showing two abrupt transitions. The first and second major step of phase transitions corresponds to a largely carrier-induced transition and largely thermally-driven full SPT, respectively. The phase transition currents,  $I_{T1}$  and  $I_{T2}$ , are labelled. Inset, small transition steps are observed near  $I_{T2}$ .

occur near the observed memory phenomenon. To prepare the device for memory writing, it was first held at a constant current bias in the insulating-monoclinic phase (M<sub>1</sub>-phase) near  $I_{T1}$ . To write the memory, an excitation, which was a weak optical pulse at a wavelength of 1550 nm in our experiment, was illuminated at normal incident. The excitation generated excess carriers to drive the VO2 into what we refer in this manuscript as the "oscillating state" (O-state). Generally, the O-state persists between  $I_{T1}$  and  $I_{T2}$  as indicated in Figure 1d. In the O-state, the device exhibits NDR (see Figure 1d) and the coexistence of the both M<sub>1</sub>-phase and metallic-rutile phase (R-phase) induces voltage oscillations, due to the periodic discharging and charging of the VO<sub>2</sub> capacitance across its IMT.[12,24] After the writing with an optical pulse, the current bias near  $I_{T1}$  was turned off within a fall-time of <150 µs. When the memorywriting bias current was applied again with a sufficiently short rise-time of <180 μs, contrary to the expectation of the VO<sub>2</sub> returning to the M<sub>1</sub>-phase, the device was consistently found in the O-state characterized by persistent voltage oscillations. The device could be reset, that is, the memory could be erased, by applying a bias current less than the hysteresis loop of the first major transition.

#### 2.1. Experimental Setup and Material Properties

Next, we discuss the details of the experimental investigation. Figure 1a shows the schematic of the device and the experimental setup (see Figure S1, Supporting Information, for more

details). The microwire VO2 device was defined using conventional microfabrication processes in a 360 nm thick VO2 film on a titanium dioxide (TiO2 (001)) substrate formed by pulsed laser deposition (PLD). Figure 1b shows a scanning electron micrograph (SEM) of a device. The VO<sub>2</sub> film on TiO<sub>2</sub> (001) substrate was strained along the c-axis by -1.2% due to the lattice mismatch,[16] which resulted in a phase transition temperature ( $T_C$ ) of ~41.5 °C (314.65 K) as shown in Figure 1c. Across the phase transition, the VO<sub>2</sub> resistivity changed by about three orders of magnitude. Room-temperature X-ray diffraction (XRD) measurement (inset of Figure 1c) confirms the composition of the material to be VO2, [28] and an atomic force microscopy shows that the film had a root-mean-square roughness of ~0.55 nm (Figure S2a, Supporting Information) and nanoscale line cracks, but the VO2 wire device was fabricated such that line cracks were avoided as shown in the SEM (Figure 1b).

## 2.2. Device Voltage-Current Characteristics

The memory measurements were conducted at room temperature and in the ambient environment. The DC VI plot for a device with VO<sub>2</sub> wire dimensions  $w \approx 1.7~\mu m$  and  $l \approx 4.7~\mu m$  is shown in Figure 1d. We ramped the current between 0 and 270  $\mu A$  in 500 nA increments with a resistor connected in series ( $R_{\rm series} = 5~{\rm k}\Omega$ ). The resistor did not affect  $I_{T1}$  and  $I_{T2}$ , but was kept in the setup so the current-biased experiments would be identical to the voltage-biased experiments in Section S1, Supporting Information (voltage-biased measurements require

a series resistance to quench the current). As can be seen in the DC VI plot, when the current was increased (solid line), the voltage across the device dropped from ~10 to ~4.7 V through the first major step of the phase transition ( $T_1$ ) at  $I_{T1} \approx 91~\mu A$  and second major step of the phase transition ( $T_2$ ) at  $I_{T2} \approx 264~\mu A$ , which constituted the full phase transition from the  $M_1$ -phase to R-phase including SPT. Much smaller transition steps existed near  $I_{T2}$  (see the inset of Figure 1d). When the current was decreased (dashed line), the reverse metal-insulator transition occurred at different currents; thus, both  $T_1$  and  $T_2$  were hysteretic, with a smaller hysteresis width for  $T_1$  and the larger hysteresis width for  $T_2$  due to the predominantly thermal-driven SPT.

#### 2.3. Nonvolatile Memory and Voltage Oscillations

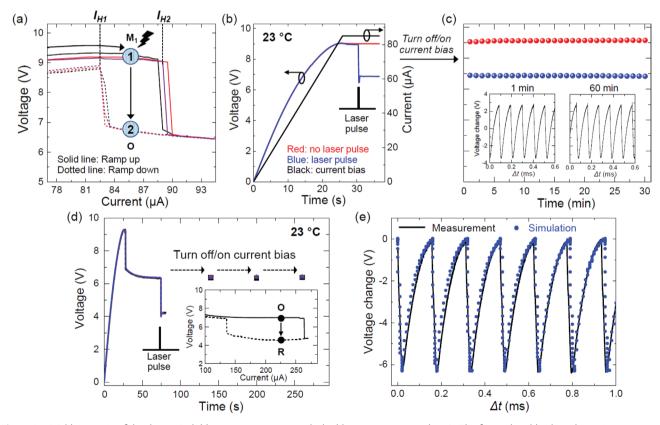

To investigate the nonvolatile memory effect, we used a combination of an electrical current bias and optical writing pulse in  $T_1$ . **Figure 2**a shows the DC VI plot of  $T_1$  of the device corresponding to Figure 1d at a temperature of 23 °C. The hysteresis loop was between  $I_{\rm H1} \approx 82.4~\mu{\rm A}$  and  $I_{\rm H2} \approx 87.6~\mu{\rm A}$ , obtained by

repeating the measurements 10 times. Before writing to the memory, we held the  $VO_2$  microwire at a current bias of  $I_B$ , which must be between  $I_{\rm H1}$  and  $I_{\rm H2}$ , at ~85  $\mu A$  ( $I_{\rm H1} < I_{\rm B} < I_{\rm H2}$ as denoted by Point 1 in Figure 2a) for ~3 s. To write to the device, we turned on a ~180 ms-long laser pulse at a wavelength of 1550 nm, incident power of ~470 µW, and with a full-width-at-half-maximum beam diameter of ~4.3 µm. The duration of the laser pulse was due to the instrumentation and can be reduced in the future using an optical modulator. The incident light induced the biased VO2 device to transition to Point 2 in Figure 2a with a DC electrical resistance reduction of  $\Delta R = 28.9 \text{ k}\Omega$  (~31.2% of the full transition) and voltage oscillations (i.e., device was in the O-state). Figure 2b shows the DC voltage measured without (red) and with (blue) an incident laser pulse. In the blue curve, even after the incident writing laser was turned off, the DC voltage readout of the device remained at ~6.9 V for at least 1 h (Figure S3, Supporting Information), indicating the voltage oscillations continued. As we will discuss in the next paragraph, this DC voltage was the average of an oscillatory signal. After we removed  $I_{\rm R}$  for an arbitrarily long period of time, we abruptly reapplied  $I_B$  to read out the device state. We measured a DC voltage of ~6.9 V during the read time

Figure 2. a) 1st hysteresis of the device (solid line: current ramp up, dashed line: current ramp down). The forward and backward transition currents are  $I_{H1}$  and  $I_{H2}$ , respectively. b) Time trace of the DC voltage across the device during a ramp up of the bias current and holding at ~85 μA (right y-axis) followed by no incident optical pulse (red), and a ~180 ms-long optical pulse at an incident optical power of ~470 μW (blue) showing optical memory writing. c) The DC voltage readout after turning off and on the current bias every 1 min. If an optical pulse was incident (blue dots) a voltage of ~6.7 V was read. If there was no light (red dots) a voltage of ~9.1 V was read. Inset, voltage oscillations corresponding to the DC voltage readout of the blue dots measured after 1 and 60 min. d) Three overlapping real-time measurements of the device voltage using a bias current at the 2<sup>nd</sup> hysteresis loop (ramp up to ~230 μA) and an incident optical pulse with power of ~1.1 mW, including turning off and on the current bias. Inset, 2<sup>nd</sup> hysteresis loop of the device. The device returned to the O-state indicated in the inset after the bias is removed. e) Simulated and measured voltage traces in the O-state. The trace is not centered at 0 V since it was captured immediately after the transition and the DC component was not yet filtered.

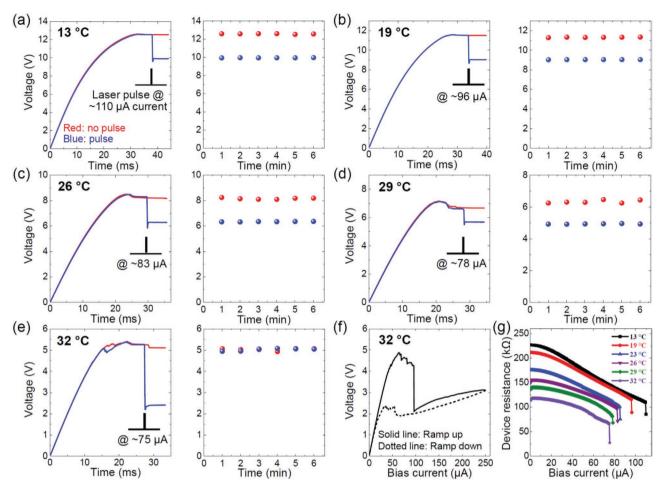

Figure 3. a—e) At temperatures ranging from 13 to 32  $^{\circ}$ C, a real-time voltage trace of the current-biased device with optical memory writing, and the tests of nonvolatile and volatile memory with the current bias turned off and on every minute. The identical optical pulse duration (~180 ms) and power (~470  $\mu$ W) were used in the measurement at 13–29  $^{\circ}$ C. An incident laser power of ~1.1 mW was used at 32  $^{\circ}$ C for full SPT. f) VI measurement at the temperature of 32  $^{\circ}$ C. g) Device resistance changes with bias currents and a light pulse at different temperatures.

even after 3 days and without any other optical or electrical input between the writing and reading steps. Figure 2c plots the first 30 min of the voltage readings with  $I_{\rm B}$  being turned on and off every minute, showing the O-state was observed every time and the memory was nonvolatile (blue dots). The red dots in Figure 2c show that when the writing optical pulse was not applied, the device remained in the  $M_{\rm 1}$ -phase with a DC voltage readout of ~9 V. This phenomenon was unique to the  $T_{\rm 1}$  transition and the current bias operation. When we repeated the experiment at room temperature by applying a bias current in the hysteresis loop of  $T_{\rm 2}$  transition (Figure 2d) or a voltage bias (Figure S4 and Supporting Information text), the device completed the SPT and functioned as a volatile memory (i.e., the R-phase did not persist without applying a current or voltage bias).

Figure 2e shows the oscilloscope time trace of the sustained voltage oscillations of the  $VO_2$  device in the O-state after the writing incident light was turned off at a bias current of  $I_B$ . The oscillations with  $I_B$  had a frequency of ~6.5 kHz and an amplitude of ~7 V, corresponding to the full voltage drop between the  $M_1$  and R phases in Figure 1d. The oscillation frequency in the absence of incident light was independent of the

optical power of the write pulse but depended on the applied current bias. In addition, as shown in the inset of Figure 2c, oscillations were repeatedly observed each time when  $I_{\rm B}$  was applied for the voltage readout. Using a circuit model for our VO<sub>2</sub> device (Section S3 and Figure S5, Supporting Information), the simulated oscillations (blue dots in Figure 2e) agree well with the measurements. The sustained oscillation frequency could be precisely tuned by the incident optical power of a continuous-wave laser after the memory writing process (Section S4 and Figure S6, Supporting Information) and was dependent on the external circuit component, such as capacitor and resistor. [12]

To test the hypothesis that the nonvolatile memory would not be present if the thermal energy was sufficiently high to enable the full insulator-metal phase transition including SPT,<sup>[29]</sup> we repeated the experiment at different temperatures and bias conditions. As the sample stage temperature was increased from 13 to 29 °C (**Figure 3**), the current bias for the phase transition decreased due to the increase in thermally generated carriers,<sup>[30]</sup> but the device could still function as a nonvolatile memory. When the sample stage was above 32 °C, the device could no longer function as a nonvolatile memory (Figure 3e), and the

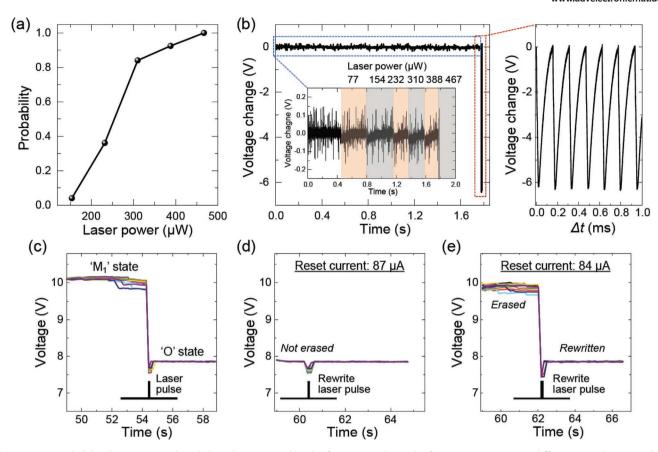

Figure 4. a) Probability that a ~180 ms-long light pulse at a wavelength of 1550 nm induces the first major transition at different optical powers. The results were determined from DC voltage measurements. b) Voltage change across the device with incident laser pulses with varying powers. The magnified plots of blue and red box regions are in the inset and right side of (b), respectively. c) Optical memory writing on a current-biased device at ~88 μA. d,e) Erasing and rewriting test with different reset bias currents. 10 measurements are overlapped.

full SPT was evident from the VI characteristic (Figure 3f). The device resistance as a function of the bias current and after an incident light pulse is shown in Figure 3g. For stage temperatures between 13 and 29 °C, the insulating VO2 (with device resistance,  $R_{\rm s} > 100 \text{ k}\Omega$ ) transitioned to the O-state (R = 65-85 $k\Omega$ ) with the application of bias current and an optical pulse. At 32 °C, however, the device fully transitioned to the R-phase (final  $R \approx 25 \text{ k}\Omega$ ). These observations are further supported by thermal simulations (Section S5 and Figure S7, Supporting Information), which show that for a substrate temperature <~30 °C, the maximum temperature reached in the device, even with an applied bias current for the  $T_1$  transition, remained below the full SPT temperature. To maintain the nonvolatile memory after the current bias is removed, the device temperature must be stabilized because the  $T_1$  hysteresis shifts with temperature. However, since the device operates near room temperature, maintaining a set device temperature should not be difficult.

#### 2.4. Threshold Optical Power

A minimum optical power was found to be necessary for memory writing and to initiate the oscillations. **Figure 4**a plots the probability of the phase transition versus the peak power of a ~180 ms-long incident light pulse with the device biased at ~86  $\mu A$ . The probability was obtained from 50 measurements at each optical power (Figure S8, Supporting Information). The phase transition probability increased with the incident optical power due to the increased photo-induced carrier generation. A threshold optical power of about 470  $\mu W$  was required for reliable writing of the VO $_2$  microwire. The inset and right side of Figure 4b show the voltage trace within the blue and red box on a magnified scale, respectively, and the sustained voltage oscillations were observed. The minimum optical power required for memory-writing can be reduced by applying a bias current closer to the transition edge.

#### 2.5. Erasing and Rewriting the Memory

To erase the VO<sub>2</sub> microwire memory, the bias current should be reduced to a value outside of the hysteresis loop of  $T_1$  transition (less than  $I_{\rm H1}$ ). After writing to the VO<sub>2</sub> microwire using a laser pulse (Figure 4c), we erased and rewrote to the device by applying reset currents and reapplying the ~180 ms-long and ~470  $\mu$ W incident laser pulse (Figures 4d,e). In this measurement, the device was initially biased at  $I_{\rm B}$  ≈88  $\mu$ A, since the hysteresis loop had slightly shifted to  $I_{\rm H1}$  ≈85  $\mu$ A and  $I_{\rm H2}$  ≈89  $\mu$ A. The reset current is the current that is applied after the initial

www.advancedsciencenews.com

ADVANCED

ELECTRONIC

MATERIALS

electrical current has been completely removed. When a reset current of ~87  $\mu$ A was applied, the VO<sub>2</sub> was not erased and stayed in the O-state because the current was greater than  $I_{\rm H1}$  (Figure 4d). For a reset current of ~84  $\mu$ A less than  $I_{\rm H1}$ , however, the erasing and rewriting processes were repeatable (Figure 4e). Finally, we determined how fast the bias current must be turned on and off to read the memory without erasing it. By applying trapezoidal waveforms with different slopes, we found that the maximum 0–100% rise/fall-time for the memory readout was about 150  $\mu$ s (Section S6 and Figure S9, Supporting Information).

#### 3. Discussion and Conclusion

The nonvolatile memory property reported in this manuscript, to our knowledge, has not been previously reported in VO<sub>2</sub>. A possible explanation for this effect is an intermediate metastable phase (M\*) in VO2 in the first major transition, even though we were not able to directly characterize this phase in this work. Without M\*, when the read current is reapplied after the writing process, the VO2 should have returned to the M<sub>1</sub>-phase and voltage oscillations would not occur. We are currently investigating the structural and dynamic properties as well as the methods to control M\*. Nevertheless, the observations here show that M\* can be leveraged to create nonvolatile memory devices. The nonvolatile memory behavior can also be addressable by a current as observed in the rise/fall-time experiments (described in Section S6 and Figure S9, Supporting Information). Thus, our VO2 device could serve as both an electronically and optically written memory with oscillations. In addition, it may be possible to write to the VO2 memory with much shorter pulses than our demonstration, potentially less than ~1 ps long. $^{[31-33]}$

The recent years have witnessed a growing number of demonstrations of VO2 memristors and VO2 oscillator networks for neuromorphic computing (see, for example, [5,8-10]). VO<sub>2</sub> memristor-based artificial neurons have been shown to be exceptionally biomimetic, exhibiting most of the known dynamics of biological neurons.<sup>[5]</sup> Image recognition has been performed by a three-oscillator-VO<sub>2</sub>-network using the phase differences between oscillations.[10] These results demonstrate the exciting computing capabilities of small networks of VO2 coupled oscillators, though thus far without the capability of in-device memory. In comparison with optically addressable memory using other phase change materials, such as Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST), our demonstration here required more optical energy (~8 µJ versus 13 to 600 pJ) for memory writing (see Table S1, Supporting Information); however, the energy could be reduced by reducing the device size, or shortening the optical pulse width. In addition, the absorbed optical energy could be significantly improved by integrating VO2 wire on optical waveguides, utilizing evanescent-wave coupling which increases the interaction length, in turn, reducing the overall optical writing energy. As well, the oscillatory property of VO2 is not present in GST, and can be exploited for oscillator-based computing. The observation of nonvolatile memory reported here can enable in-device memory in VO<sub>2</sub> to simplify system architectures and open new concepts for phase-change photonics and electronics.

## 4. Experimental Section

Device Fabrication: A 360 nm thick VO<sub>2</sub> film was formed on a titanium dioxide (TiO<sub>2</sub> (001)) substrate by pulsed laser deposition (PLD) using a VO<sub>2</sub> target at a temperature of 380 °C. The devices were fabricated using aligned electron-beam lithography (EBL), dry etching, and metal deposition. First, 20 μm × 20 μm tungsten alignment markers for the EBL were sputtered onto the VO2 film. Microwires, each of which is connected to rectangular areas of size 3  $\mu\text{m}\times48~\mu\text{m}$ at the two ends forming "H" shaped regions, were written by EBL (Raith EBPG 5000+) using ZEP-520A positive tone resist and then inductively coupled plasma-reactive ion etching (ICP-RIE) was carried out. The rectangle/square at the two ends of the wires provides a large surface area between the VO2 and the contact pads. A gas mixture of CF<sub>4</sub> (10 sccm) and Ar (20 sccm) at a total pressure of 50 mTorr was used. For a fully etched VO2, an ICP power of 300 W and RF power of 50 W was applied for 30 s. Microwires with varying lengths of 2–5 μm and widths of 1–3 μm were fabricated. Finally, palladium (Pd) electrical contact pads were formed atop of the VO2 through EBL, thermal evaporation deposition, and lift-off processes. Pd was chosen for electrical contacts with the VO2 due to the low work function mismatch.

Measurement Setup: The experimental setup is illustrated in Figure S1, Supporting Information. The sample was mounted on a temperature-controlled stage and accurately adjusted by a thermoelectric cooler (TEC) controller (5235 TEC Source, Arroyo Instruments) to 0.01 °C. The memory tests were performed in ambient conditions at temperatures ranging between 13 and 32 °C. The sourcing and measuring of device current/voltage were accomplished by contacting tungsten probes to the two Pd pads using a precision SourceMeter (2636A SourceMeter, Keithley) with a  $R_{\rm series} = 5 \text{ k}\Omega$ resistor in series, which protected the device from being overdriven during the phase transition. For the optical addressing of the device, a 1550-nm-wavelength optical beam from a tunable laser source (81600B, Agilent) was focused on the VO<sub>2</sub> wire through a 100× objective lens. The full-width at half maximum (FWHM) beam spot diameter was  $\sim$ 4.3  $\mu$ m and the incident laser power on the device ranged from 80  $\mu$ W to 2.5 mW. The incident laser pulses were ~180 ms-long, limited by the time to turn the laser on and off via SCPI commands. A silicon CCD visible and InGaAs infrared cameras were used to align the device and laser beam spot, respectively. The generated voltage waveforms were measured by a 1 GHz bandwidth oscilloscope (InfiniiVision DSOX3104A, Keysight) connected to a  $C_{\rm ext} = 10$  nF capacitor in parallel with the  $VO_2$  device including  $R_{\text{series}}$  via a 6 MHz oscilloscope probe (Tektronix 2220, 1× mode) (Figure S1b, Supporting Information). In Figure 2e and Figure 4b, the DC offset is not removed due to RC transients.

## **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

### Acknowledgements

Y.J. and J.J. contributed equally to this work. The authors thank A. Sharma and Y. Yang for help with device measurements. The external funding sources were Natural Sciences and Engineering Research Council of Canada and the Canada Research Chair program.

Open access funding enabled and organized by Projekt DEAL.

#### **Conflict of Interest**

The authors declare no conflict of interest.

www.advancedsciencenews.com

## ADVANCED ELECTRONIC MATERIALS

## **Data Availability Statement**

Research data are not shared.

## **Keywords**

nonvolatile memories, oscillators, vanadium dioxide

Received: November 20, 2020 Revised: May 16, 2021 Published online:

- [1] J. Backus, Commun. ACM 1978, 21, 613.

- [2] D. Kuzum, R. G. Jeyasingh, B. Lee, H.-S. P. Wong, Nano Lett. 2012, 12, 2179.

- [3] C. D. Wright, P. Hosseini, J. A. V. Diosdado, Adv. Funct. Mater. 2013, 23, 2248.

- [4] M. D. Pickett, G. Medeiros-Ribeiro, R. S. Williams, Nat. Mater. 2013, 12, 114.

- [5] W. Yi, K. K. Tsang, S. K. Lam, X. Bai, J. A. Crowell, E. A. Flores, *Nat. Commun.* 2018, 9, 4661.

- [6] J. Feldmann, N. Youngblood, C. Wright, H. Bhaskaran, W. Pernice, Nature 2019, 569, 208.

- [7] J. del Valle, P. Salev, F. Tesler, N. M. Vargas, Y. Kalcheim, P. Wang, J. Trastoy, M.-H. Lee, G. Kassabian, J. G. Ramírez, *Nature* 2019, 569, 388

- [8] N. Shukla, A. Parihar, E. Freeman, H. Paik, G. Stone, V. Narayanan, H. Wen, Z. Cai, V. Gopalan, R. Engel-Herbert, Sci. Rep. 2014, 4, 4964.

- [9] A. Parihar, N. Shukla, S. Datta, A. Raychowdhury, J. Appl. Phys. 2015, 117, 054902.

- [10] E. Corti, A. Khanna, K. Niang, J. Robertson, K. E. Moselund, B. Gotsmann, S. Datta, S. Karg, *IEEE Electron Device Lett.* 2020, 41, 629.

- [11] F. Morin, Phys. Rev. Lett. 1959, 3, 34.

- [12] H.-T. Kim, B.-J. Kim, S. Choi, B.-G. Chae, Y. W. Lee, T. Driscoll, M. M. Qazilbash, D. Basov, J. Appl. Phys. 2010, 107, 023702.

- [13] A. Joushaghani, J. Jeong, S. Paradis, D. Alain, J. S. Aitchison, J. K. Poon, *Photonics* 2015, 2, 916.

- [14] A. Cavalleri, C. Tóth, C. W. Siders, J. Squier, F. Ráksi, P. Forget, J. Kieffer, Phys. Rev. Lett. 2001, 87, 237401.

- [15] B. Zhi, G. Gao, H. Xu, F. Chen, X. Tan, P. Chen, L. Wang, W. Wu, ACS Appl. Mater. Interfaces 2014, 6, 4603.

- [16] J. Jeong, N. Aetukuri, T. Graf, T. D. Schladt, M. G. Samant, S. S. Parkin, *Science* 2013, 339, 1402.

- [17] H. Yoon, M. Choi, T.-W. Lim, H. Kwon, K. Ihm, J. K. Kim, S.-Y. Choi, J. Son, Nat. Mater. 2016, 15, 1113.

- [18] K. Shibuya, A. Sawa, Adv. Electron. Mater. 2016, 2, 1500131.

- [19] T. Driscoll, H.-T. Kim, B.-G. Chae, M. Di Ventra, D. Basov, Appl. Phys. Lett. 2009, 95, 043503.

- [20] L. Pellegrino, N. Manca, T. Kanki, H. Tanaka, M. Biasotti, E. Bellingeri, A. S. Siri, D. Marré, Adv. Mater. 2012, 24, 2929.

- [21] S. H. Bae, S. Lee, H. Koo, L. Lin, B. H. Jo, C. Park, Z. L. Wang, Adv. Mater. 2013, 25, 5098.

- [22] A. Beaumont, J. Leroy, J.-C. Orlianges, A. Crunteanu, J. Appl. Phys. 2014, 115, 154502.

- [23] N. Manca, L. Pellegrino, T. Kanki, W. J. Venstra, G. Mattoni, Y. Higuchi, H. Tanaka, A. D. Caviglia, D. Marré, Adv. Mater. 2017, 29, 1701618.

- [24] S. M. Bohaichuk, S. Kumar, G. Pitner, C. J. McClellan, J. Jeong, M. G. Samant, H.-S. P. Wong, S. S. Parkin, R. S. Williams, E. Pop, Nano Lett. 2019, 19, 6751.

- [25] G. Stefanovich, A. Pergament, D. Stefanovich, J. Phys.: Condens. Matter 2000, 12, 8837.

- [26] J. I. Sohn, S. N. Cha, S. B. Son, J. M. Kim, M. E. Welland, W.-K. Hong, *Nanoscale* 2017, 9, 8200.

- [27] K. Nagashima, T. Yanagida, H. Tanaka, T. Kawai, Phys. Rev. B 2006, 74, 172106.

- [28] L. Fan, S. Chen, Z. Luo, Q. Liu, Y. Wu, L. Song, D. Ji, P. Wang, W. Chu, C. Gao, *Nano Lett.* 2014, 14, 4036.

- [29] D. Lee, B. Chung, Y. Shi, G.-Y. Kim, N. Campbell, F. Xue, K. Song, S.-Y. Choi, J. P. Podkaminer, T. H. Kim, P. J. Ryan, J.-W. Kim, T. R. Paudel, J.-H. Kang, J. W. Spinuzzi, D. A. Tenne, E. Y. Tsymbal, M. S. Rzchowski, L. Q. Chen, J. Lee, C. B. Eom, Science 2018, 362, 1037.

- [30] H.-T. Kim, B.-G. Chae, D.-H. Youn, S.-L. Maeng, G. Kim, K.-Y. Kang, Y.-S. Lim, New J. Phys. 2004, 6, 52.

- [31] A. Cavalleri, T. Dekorsy, H. H. W. Chong, J. C. Kieffer, R. W. Schoenlein, Phys. Rev. B 2004, 70, 161102.

- [32] P. Baum, D.-S. Yang, A. H. Zewail, Science 2007, 318, 788.

- [33] Z. Yang, C. Ko, S. Ramanathan, Annu. Rev. Mater. Res. 2011, 41, 337.