# Model Checking for a Multi-Execution Memory Model

EVGENII MOISEENKO, JetBrains Research, Serbia MICHALIS KOKOLOGIANNAKIS, MPI-SWS, Germany VIKTOR VAFEIADIS, MPI-SWS, Germany

Multi-execution memory models, such as Promising and Weakestmo, are an advanced class of weak memory consistency models that justify certain outcomes of a concurrent program by considering multiple candidate executions collectively. While this key characteristic allows them to support effective compilation to hardware models and a wide range of compiler optimizations, it makes reasoning about them substantially more difficult. In particular, we observe that Promising and Weakestmo inhibit effective model checking because they allow some suprisingly weak behaviors that cannot be generated by examining one execution at a time.

We therefore introduce Weakestmo2, a strengthening of Weakestmo by constraining its multi-execution nature, while preserving the important properties of Weakestmo: DRF theorems, compilation to hardware models, and correctness of local program transformations. Our strengthening rules out a class of surprisingly weak program behaviors, which we attempt to characterize with the help of two novel properties: *load buffering race freedom* and *certification locality*. In addition, we develop WMC, a model checker for Weakestmo2 with performance close to that of the best tools for per-execution models.

$\label{eq:concepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:oncepts:o$

Additional Key Words and Phrases: Weak memory models, model checking

#### **ACM Reference Format:**

Evgenii Moiseenko, Michalis Kokologiannakis, and Viktor Vafeiadis. 2022. Model Checking for a Multi-Execution Memory Model. *Proc. ACM Program. Lang.* 6, OOPSLA2, Article 152 (October 2022), 28 pages. https://doi.org/10.1145/3563315

#### 1 INTRODUCTION

A *weak memory model* is a formal definition of the semantics of shared-memory concurrent programs, which allows more program outcomes (i.e., reachable thread configurations) than can be explained by a straightforward interleaving of the threads of a program. Consider, for instance, the load-buffering (LB) program below. (In our examples, we assume all variables are initialized to 0.)

$$r_1 := x \text{ // reads } 1$$

|  $r_2 := y \text{ // reads } 1$  |  $x := r_2$  (LB)

The annotated outcome, where both threads read the value 1, cannot be explain by simply interleaving the instructions of the two threads, since the first instruction to execute can only read 0 (the initial value). Multicore Arm processors, however, do exhibit this outcome because they often execute independent instructions out of order. For example, Thread 1 may first perform the y := 1 write, then Thread 2 can read y = 1 and write x := 1, and then Thread 1 can finish by reading x = 1.

Authors' addresses: Evgenii Moiseenko, JetBrains Research, Serbia, evgeniy.moiseenko@jetbrains.com; Michalis Kokologiannakis, MPI-SWS, Germany, michalis@mpi-sws.org; Viktor Vafeiadis, MPI-SWS, Germany, viktor@mpi-sws.org.

This work is licensed under a Creative Commons Attribution 4.0 International License.

© 2022 Copyright held by the owner/author(s).

2475-1421/2022/10-ART152

https://doi.org/10.1145/3563315

Most memory models—including all those for hardware architectures—are defined in a *per-execution* style, where each possible program outcome is explained by a single program execution witnessing that outcome. As Batty et al. [2015] have shown, however, this per-execution style is inadequate for defining the semantics of programming languages like C/C++ that strive to provide features with optimal efficiency.

For this reason, advanced language-level memory models (e.g., [Chakraborty et al. 2019; Jagadeesan et al. 2020; Jeffrey et al. 2016; 2022; Kang et al. 2017; Manson et al. 2005; Paviotti et al. 2020; Pichon-Pharabod et al. 2016]) instead adopt a *multi-execution* style, where multiple candidate program executions are used together to justify a given program outcome. For example, Promising [Kang et al. 2017] achieves this by augmenting the regular in-order program execution with an additional step: a promise to execute a future write that is backed up with an additional execution justifying that it is possible to fulfill the promise. Promising explains the LB outcome as follows. Thread 1 first promises to write y := 1, which is fulfillable by running the thread to completion. Then Thread 2 reads 1 and writes x := 1, and then Thread 1 reads 1, arriving at the desired outcome. The fact that promises have to be justified by other promise-free executions is what makes Promising a multi-execution model. And this aspect of Promising is crucial: removing promise certification would lead to an overly weak model that would allow some clearly undesirable outcomes known as 'out-of-thin-air' outcomes in the literature. Other multi-execution models, such as Weakestmo [Chakraborty et al. 2019], explain the LB outcome in a similar way, but explicitly represent the multiple program executions as an event structure.

While multi-execution models, such as Promising and Weakestmo, can be implemented efficiently on a wide range of hardware architectures [Moiseenko et al. 2020; Podkopaev et al. 2019], they have a significant drawback: they are very difficult to reason about, especially in an automated fashion. Although there are numerous effective automated techniques for verifying programs under per-execution weak memory models (e.g., [Abdulla et al. 2015a; 2018; 2015b; Barnat et al. 2013; Bouajjani et al. 2013; Demsky et al. 2015; Huang et al. 2016; Kokologiannakis et al. 2017; 2019]), there are no automated techniques for reasoning about multi-execution models. Verification of finite-state programs (with loops) is undecidable [Abdulla et al. 2021], and even model checking (i.e., enumerating all possible outcomes) of small loop-free programs is typically intractable.

We believe that the difficulty in automated verification on multi-execution models is largely due to the unconstrained nature of the models' out-of-order execution mechanisms. To make such a model amenable to model checking, one has to constrain the use of multiple executions in two distinct ways: (1) on *when* multiple executions are introduced to explain a certain behavior (i.e., in terms of Promising, when a promise can be made); and (2) on *how much* these multiple executions interact with one another. Naturally, we desire to restrict multi-execution nature as much as possible: additional executions should only be allowed when there is a good reason to do so, and they should not be allowed to diverge too much from one another.

Our first contribution is to propose two properties that constrain multiple executions in the aforementioned ways, namely *load buffering race freedom* and *certification locality* (§2). Besides their use for model checking, these properties rule out certain program outcomes that cannot be observed by any combination of reasonable compiler optimizations on existing hardware platforms, and so may be of independent interest.

Subsequently, we introduce Weakestmo2, a strengthening of Weakestmo [Chakraborty et al. 2019] that satisfies load buffering race freedom and certification locality (§3). Further, we show that Weakestmo2 preserves the soundness of Weakestmo's efficient compilation schemes to hardware-level models shown by Moiseenko et al. [2020] (§3.4) as well as the soundness of local program transformations (§3.5).

Finally, we develop an effective model checking algorithm, WMC, for verifying programs running on Weakestmo2 (§4), and implement it as an extension of the GenMC model checker [Kokologiannakis et al. 2019; 2021]. Our experiments (§5) demonstrate that WMC's performance is superior to that of the few other tools for (per-execution) weak memory models admitting the LB behavior (i.e., the annotated outcome of the LB program), and comparable to the best tools for models that forbid the LB behavior.

#### 2 OVERVIEW

In this section, we recall the basic terminology of weak memory models (§ 2.1) and motivate our Weakestmo2 model. For the latter, we introduce two properties of multi-execution models that are needed for effective model checking but are not satisfied by Promising and Weakestmo.

**Load buffering race freedom** (LBRF, §2.2) restricts the multi-execution nature of a model to affect only programs with *load buffering races* (LB races). LBRF is defined analogously to the well-known *data race freedom* (DRF) guarantee [Adve et al. 1996; Manson et al. 2005] replacing the notion of a data race with a stronger novel notion of an LB race.

Certification locality (CL, §2.3) concerns multi-execution models with a certification mechanism and restricts *how much* certification executions can differ from the main execution. CL allows one to determine locally whether a certain load-store reordering is allowed, which disallows certain 'bait-and-switch' behaviors [Jagadeesan et al. 2020].

We conclude this section by explaining how these properties enable effective model checking (§2.4).

# 2.1 Execution Graphs and Data Race Freedom

In the literature of axiomatic (a.k.a. declarative) per-execution memory models, the possible executions of a program P under a model M are represented as a set of *execution graphs* that correspond to the instructions of P and satisfy M's consistency predicate. Execution graphs consist of:

- a set of nodes, called *events*, which represent the individual operations performed by the program that are relevant for concurrency (e.g., reads R, writes W, fences F), and

- various kinds of directed edges between events, such as:

- the *program order* (po), relating events in the same thread in their control-flow order as well as initialization events before other events, and depicted as a solid black edge;

- the *reads-from* (rf) relation, connecting each read to the write it is reading from, and depicted as a dashed green edge from the write to the read;

- the *happens-before* (hb) order, a subset of porf  $\triangleq$  (po  $\cup$  rf)<sup>+</sup> that includes po, capturing ordering due to intra-thread control-flow and inter-thread synchronization. (For simplicity, the examples of this paper do not contain inter-thread synchronization, and so hb = po.)

The strongest useful model in this framework is *sequential consistency* (SC) [Lamport 1979], which requires that there be a total order  $<_{SC}$  among all events of an execution graph extending porf such that each read reads from the most recent same-location write that precedes it in  $<_{SC}$ . Other models place weaker constraints, with models such as x86-TSO [Owens et al. 2009] and RC11 [Lahav et al. 2017] requiring (among other things) that porf be acyclic.

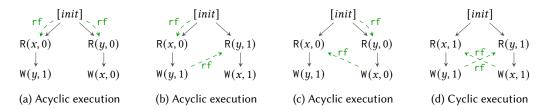

Figure 1 shows four execution graphs corresponding to the LB program from §1. These graphs are generated by picking every possible value for each read event that matches the value written by the write event to the same location whence the read is reading from. The first three graphs are SC-consistent (and therefore also RC11-consistent). By contrast, the fourth graph, witnessing the "load buffering" behavior, is not RC11-consistent because it contains a porf cycle.

A standard property that is expected of memory models is the DRF<sub>SC</sub> guarantee [Adve et al. 1996; Manson et al. 2005], which constrains non-SC behaviors to occur only on programs with data

Fig. 1. Execution graphs of LB.

races. We say that two events (of different threads) are *concurrent* if they are not ordered by hb. A pair of events form a *data race* in an execution graph if they are concurrent memory accesses to the same location, at least one of which is a write event. A program *P* is *data-race-free* under a memory model *M* if no consistent execution graph of *P* under *M* contains a data race.

Definition 2.1 (DRF). A memory model M provides the data race freedom guarantee with respect to a stronger memory model M' (written  $DRF_{M'}$ ) if, for any data-race-free program P under M', its consistent executions under M are exactly the same as under M'.

A memory model providing the DRF<sub>SC</sub> guarantee allows programmers to adopt a defensive programming strategy of avoiding data races (e.g., by using locks), which incurs some performance degradation but relieves them from the need to learn and understand the memory model definition.

# 2.2 Load Buffering Race Freedom

Load buffering race freedom is analogous to DRF. We say that a po edge between a read and a write is *reorderable* (rpo) if the two accesses are *relaxed* following C11 terminology (i.e., weaker than release/acquire) and there is no fence between them. A reorderable edge signifies that the two events may be executed out of order (e.g., under Promising [Kang et al. 2017], the write may be promised), and thus contribute to a load buffering behavior.

Definition 2.2 (Load buffering race). A pair of events r and w form a load buffering race (LB race) in an execution graph if r is a read, w is a concurrent write to the same location, and there is a rpo; (rf\po); porf path from r to w (i.e., a porf-path starting with a reorderable edge).

For instance, execution graph (b) of Fig. 1 has a load buffering race between the R(x, 0) and W(x, 1) events. Similarly, graph (c) has an LB race between the R(y, 0) and W(y, 1) events.

Existence of a porf-path between w and r indicates that the write might depend on the read. In models like RC11, it means that r cannot read from w because that would create a porf-cycle, such as the one in Fig. 1(d). We insist that the first edge along this path is reorderable to rule out cases where an explicit fence has been added to prevent the load-buffering behavior.

Definition 2.3 (LB-race-free program). A program P is LB-race-free under a memory model M if no consistent execution graph of P under M contains a load buffering race.

Definition 2.4 (LBRF). A memory model M provides the load buffering race freedom guarantee with respect to a stronger memory model M' (written LBRF $_{M'}$ ) if, for any LB-race-free program P under M', its consistent executions under M are exactly the same as under M'.

Normally, we take M' to be some standard model that forbids porf-cycles, such as RC11 . Similar to DRF, LBRF<sub>RC11</sub> allows one to program defensively against a model M without even knowing its definition by avoiding LB races. Since absence of LB races is to be checked with respect to RC11, one can use any of the existing tools and methodologies that reason about program correctness

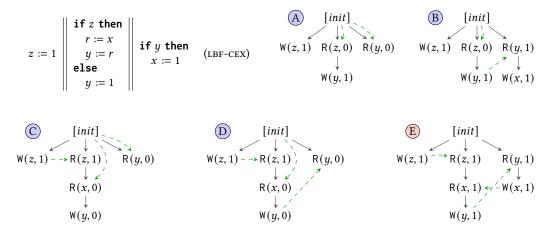

Fig. 2. A program with its RC11-consistent execution graphs and a problematic cyclic execution.

under RC11 (e.g., iGPS, Herd, RCMC, GENMC, etc). Moreover, LB races can easily be removed by making the porf-paths from the racy read to the write start with non-reorderable edges. This can be achieved, for example, by strengthening the access mode of the read to be an acquire or by adding an acquire or release fence right after it. In § 5.4, we report on a script that does so automatically. Based on the results of Ou et al. [2018] and our experience, the run-time overhead incurred by these extra fences is extremely low, if at all perceptible.

2.2.1 LBRF and Existing Models. Among the axiomatic per-execution models that allow LB behaviors, the original C11 model [Batty et al. 2011] does not satisfy LBRF<sub>RC11</sub> because it allows out-of-thin-air outcomes and does not even satisfy DRF<sub>SC</sub>. Lower-level models that track syntactic dependencies between instructions, such as IMM [Podkopaev et al. 2019], Power [Alglave et al. 2014], and ARM-8 [Pulte et al. 2018], satisfy LBRF wrt. their strengthenings with porf-acyclicity. The additional behaviors they allow over their strengthenings are porf-cycles with at least one po edge from a load to a store being reorderable. By changing the rf edge of that load to read from a prior store, and relying on "receptiveness" of the mapping from programs to executions, we can construct an LB race. As an example of this reasoning, we prove the following theorem:

Among the multi-execution models, Promising [Kang et al. 2017; Lee et al. 2020] and Weakestmo [Chakraborty et al. 2019] do not satisfy LBRF<sub>RC11</sub>. To see this, consider the LBF-CEX program along with its executions shown in Fig. 2. Although none of its RC11-consistent executions ( $\mathbb{A}$ ), ( $\mathbb{B}$ ), ( $\mathbb{C}$ ), ( $\mathbb{D}$ ) contains an LB race, both Promising and Weakestmo allow the additional execution ( $\mathbb{E}$ ) where r gets the value 1. This execution can arise in the following manner. First, thread 2 promises the W(y, 1) store; the promise is allowed because thread 2 can read z=0 and fulfill it. Then, thread 3 executes: it reads y=1 and writes 1 to x. Finally, threads 1 and 2 execute: thread 2 reads z=1 and x=1, and subsequently writes 1 to y thereby fulfilling its promise.

That said, it is fairly straightforward to strengthen Promising and Weakestmo to satisfy LBRF by restricting when promises can be made. The existing condition of Promising requires there to be a thread-local execution that certifies the promise. In addition to that, we can require there to be an execution witnessing an LB race. As we shall shortly see, however, satisfying LBRF alone is not

sufficient for effective model checking. We need another locality property that completely forbids non-local certifications that depend on external writes like the z = 1 write in the example above.

## 2.3 Certification Locality

LBRF restricts *when* writes may be promised (i.e., only upon LB races), but not *how*. In models like Promising and Weakestmo (even if artificially strengthened to satisfy LBRF), certifications of outstanding promises can differ a lot from the actual executions whose promises they are certifying. As we will shortly see, this leads to some rather weak outcomes.

We start with an example that does not directly constitute an odd behavior but that is indicative of what can go wrong with non-local certifications.

$$x := 1 \quad \left\| \begin{array}{c} r_1 := x \text{ $/\!\!/$ reads 1} \\ y := r_1 \end{array} \right\| \begin{array}{c} r_2 := y \text{ $/\!\!/$ reads 1} \\ x := r_2 \end{array} \qquad \begin{array}{c} \text{(init)} \\ \text{R}(x,1) \\ \text{R}(x,1) \\ \text{R}(y,1) \\ \text{W}(y,1) \end{array} \qquad \text{(LB+DEP+W)}$$

The annotated outcome is perfectly valid if Thread 2 gets the value 1 from Thread 1 and propagates it to Thread 3—this outcome is even allowed under SC. What is odd, however, is to justify the outcome by the depicted execution graph, where Threads 2 and 3 read from each other without any flow of information from Thread 1 to either of these threads. The problem is that both Promising and Weakestmo essentially allow this justification. After executing Thread 1, Thread 2 can promise to write 1 to y (by reading from Thread 1). Thread 3 then executes to completion, reading from Thread 2, and writing 1 to x. Finally, Thread 2 continues, reads from Thread 3 and fulfills its promise, thus resulting in the graph above. What went wrong in this execution is that, while the write of Thread 1 was needed to enable the early execution of the write in Thread 2, this dependency is then forgotten in the final execution.

Certification locality forbids exactly this pattern. We say that a write is non-local at a certain point in a thread if it neither happens-before that point nor is read by an event happening-before that point. CL requires that every non-local write that is read in the process of certifying a promise also be read by the same thread while issuing the promise and vice versa. In other words, the two executions of the thread issuing a promise should read exactly the same non-local writes between the point the promise is issued (i.e., when the executions start diverging because they read from different writes) and the points where the promises are fulfilled.

To further justify CL, we next show an example of a really weak behavior allowed by Promising and Weakestmo. Consider the LB+LOOP program below and the associated execution graph that reads an arbitrary natural number n into  $r_1$  and  $r_2$ .

$$\begin{aligned} r_1 &:= x \\ \text{for } i &:= 0 \text{ to } r_1 \\ y &:= i+1 \end{aligned} \quad \begin{aligned} r_2 &:= y \\ \text{for } j &:= 1 \text{ to } r_2 \end{aligned} \quad \underbrace{\begin{bmatrix} \text{R}(x,n) \neq \text{W}(y,1) \rightarrow \text{W}(y,2) \rightarrow \cdots \rightarrow \text{W}(y,n) \rightarrow \text{W}(y,n+1) \\ \vdots \\ \text{R}(y,n) \neq \text{W}(x,1) \rightarrow \text{W}(x,2) \rightarrow \cdots \rightarrow \text{W}(x,n) \end{aligned}} \quad \underbrace{(\text{LB+LOOP})}_{\text{LB+LOOP}}$$

The displayed outcome is allowed by Promising (and similarly by Weakestmo) because Thread 1 can initially promise y := 1 (which it can trivially fulfill), then Thread 2 can promise x := 1 (which it can fulfill by reading y = 1 from Thread 1), then Thread 1 can promise y := 2 (by reading y = 1), then Thread 2 can promise y := 2 and so on. Again, the problem in this unbounded execution is the lack of certification locality. Once a thread depends on an external write to justify a promise, it should not "change its mind" and ignore that write in favor of a different one.

2.3.1 Enforcing CL. Repairing Promising to satisfy CL is not as straightforward as it is for LBRF because it does not track the exact set of writes read by a thread. We therefore instrument the Promising state by attaching to each promise a set of external writes that must be read before fulfilling the promise. We then check that as long as a thread contains outstanding promises, it can only read from external writes that are recorded in its promise set and, moreover, that when a promise is fulfilled all its attached external writes have been read. We present a suitable definition in [Moiseenko et al. 2022, B]. While our adapted definition achieves certification locality, we have not investigated whether it also satisfies the remaining properties of the original Promising model, namely correctness of compilation and source-to-source transformations.

By contrast, repairing Weakestmo is much easier because the certification runs are available as part of the event structure. To enforce CL, one can simply augment the Weakestmo definition with an axiom that rules out 'bait-and-switch' behaviors. We defer the formal definition of our resulting model, Weakestmo2, to  $\S 3$ . There we also establish three important results about Weakestmo2: it provides the LBRF<sub>RC11</sub> and DRF<sub>SC</sub> guarantees ( $\S 3.3$ ), its expected compilation schemes to hardware models are sound ( $\S 3.4$ ), and it supports the expected local reorderings and eliminations ( $\S 3.5$ ).

# 2.4 WMC: Effective Model Checking for Multi-Execution Memory Models

Apart from serving as criteria to rule out certain weak behaviors of multi-execution memory models, LBRF and CL are instrumental in making model checking of programs on such models feasible. We briefly describe how WMC, our model checking algorithm for Weakestmo2, exploits these properties. (We defer the full presentation of WMC to §4.)

Stateless model checkers, such as GenMC [Kokologiannakis et al. 2019], generate all the consistent executions of a given program in an incremental fashion. Starting with the empty execution graph, they add one event at a time in all possible consistent ways. With multi-execution memory models, there are two ways in which events can be added: either by adding events in order or by promising a write out of order. Considering all possible promises, however, is infeasible because of the huge state-space that would need to be explored.

This is where LBRF helps: Promises only need to be considered when an LB race is encountered. WMC therefore first generates the RC11-consistent executions of a program using techniques from the literature. Whenever it discovers an LB race, it uses an additional promising/certification mechanism to explore executions with porf cycles. As an example of how WMC works at a high level, consider the LB program from §1. Under RC11, LB has 3 consistent executions (Figures 1a to 1c), and WMC starts by enumerating those. While doing so, however, it notices that the execution of Fig. 1b contains a load buffering race between events R(x,0) and W(x,1). Thus, WMC creates the execution of Fig. 1d by *promising* the write W(y,1) in Thread 1 (so that R(y,1) can read from it), and then by making R(x,0) read from W(x,1). Subsequently, it *certifies* the promised write in Thread 1, and generates the cyclic execution.

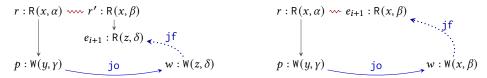

This is exactly the point where CL is useful: It ensures that a promise can quickly be certified or withdrawn by executing only the thread containing the racy read. We illustrate this point with the program below, which is a slight variant of LBF-CEX with the reads of x and z swapped in Thread 2. This program has an acyclic execution with an LB race on the x accesses (shown to the side), and so the model checker will have to consider promising W(y, 1) in Thread 2.

The model checker will then try to certify the promise by re-executing Thread 2 when it reads 1 for x. The only way to certify the promise is by reading from W(z, 1). However, depending on the scheduling strategy, this write might not be available at the point when the LB race was detected. Therefore, to avoid missing any executions, the model checker would have to postpone the certification of W(y, 1) and first explore other parts of the program, an exploration which may itself involve more promises and certifications. This approach is not only complicated to implement correctly, but also rather inefficient because in the fairly common case that the promise cannot be certified, one would wastefully explore all the possible executions of other parts of the program, leading to many blocked explorations.

CL enables a crucial optimization: Since (under CL) certification runs can read only from writes in the porf-prefix of the promise (see §3), the promise can be certified *locally* and *immediately* by re-executing the thread in question. In our example, regardless of whether W(z, 1) has been added to the graph or not, WMC will only consider the read R(z, 0), and therefore conclude that the promise W(y, 1) cannot be certified.

As we show in §5, our technique for promising writes *only* upon detecting an LB race and certifying promised writes *immediately* and *locally* scales much better than the existing techniques that tackle similar memory models. Indeed, the few existing model checkers that handle such models (e.g., [Norris et al. 2013; Pulte et al. 2019]) explore all possible certifiable promises, irrespective of whether they result in additional behaviors. Such wasteful blind exploration of promises is the key factor contributing to their poor performance.

Further, the optimization due to LBRF can also be used to improve by a moderate amount model checking on per-execution models that allow LB behaviors, such as IMM. To demonstrate this, we took HMC [Kokologiannakis et al. 2020], a model checker that operates under IMM, and implemented HMC<sub>LBRF</sub>, a version of HMC that leverages LBRF. Similarly to WMC, HMC<sub>LBRF</sub> starts by enumerating RC11-consistent executions, and falls back to dependency tracking only upon detecting an LB race. As we show in  $\S$ 5, HMC<sub>LBRF</sub> outperforms HMC in LB-race-free programs, thereby further showcasing LBRF's usefulness in verification.

#### 3 REPAIRING WEAKESTMO

In this section, we describe how Weakestmo2, our strengthening of Weakestmo, supports LBRF and CL. In what follows, we assume a simplified version of the model, containing only relaxed accesses and fences. For the full model, we refer the reader to Chakraborty et al. [2019] and [Moiseenko et al. 2022, p. C].

Weakestmo is an axiomatic multi-execution memory consistency model. Unlike conventional axiomatic models, which determine the validity of particular outcome based on a consistency predicate on a single execution graph, Weakestmo considers the execution graph consistent if it can be extracted from some consistent *event structure*. Event structures encompass multiple runs of a program in a single graph. That is, event structures can contain several execution branches of the same thread, which are used to model the speculative out-of-order execution of instructions.

Definition 3.1. An event is a tuple  $\langle id, tid, lab \rangle$  where  $id \in \mathbb{N}$  is a unique identifier for the event,  $tid \in \mathbb{N}_{\perp}$  identifies the thread to which the event belongs ( $\perp$  for initialization events), and lab is a *label* of the form: (1) R(x, v) for a read of  $v \in Val$  from  $x \in Loc$ ; (2) W(x, v) for a write of  $v \in Val$  to  $x \in Loc$ ; (3) F for a fence.

We write Event for the set of all events. The set of all reads is  $R \triangleq \{\langle i, t, l \rangle \mid l = R(.)\}$ . The sets of all writes and fences are defined analogously. Given an event e, we write id(e), tid(e), and lab(e) to project its components, and loc(e) and val(e) to project its location and value respectively.

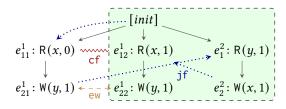

Fig. 3. LB event structure and an extracted execution.

Further, given a relation r, we use dom(r) and rng(r) to denote its domain and codomain, while  $r^?$ ,  $r^+$ , and  $r^*$  denote its reflexive, transitive, and reflexive-transitive closures, respectively. We write  $r^{-1}$  for the inverse of r, [A] for the identity relation  $\{(a,a) \mid a \in A\}$ ,  $r_1; r_2$  for the composition of  $r_1$  and  $r_2$ :  $\{(a,b) \mid \exists c \ (a,c) . \in r_1 \land (c,b) \in r_2\}$ , and  $r|_s$  for the restriction of r onto set  $s: r|_s \triangleq r \cap s \times s$ . When f is a function, we define  $=_f \triangleq \{(a,b) \mid f(a) = f(b) \neq \bot\}$ .

*Definition 3.2.* An *event structure S* is a tuple with the following components:

- E ⊆ Event is a set of events with unique identifiers that includes initialization events, writing 0 to each memory location used by the program.

- po  $\subseteq$  E  $\times$  E is the *program order*, which captures the order of events of the same thread according to the program's control flow, and orders initialization events before all other events. Because an event structure can contain multiple runs of one thread, po does not have to be total among the events of the same thread. Events of the same thread unordered by po are said to be in *conflict*:  $\mathsf{cf} \triangleq =_{\mathsf{tid}} \setminus (\mathsf{po} \cup \mathsf{po}^{-1})^?$ . Two events are in *immediate conflict* if they are in conflict but their predecessors are not:  $\mathsf{cf}|_{\mathsf{imm}} \triangleq \mathsf{cf} \setminus (\mathsf{cf} ; \mathsf{po} \cup \mathsf{po}^{-1} ; \mathsf{cf})$ .

- jf ⊆ [W]; (=<sub>loc</sub> ∩ =<sub>val</sub>); [R] is the *justified from* relation, which maps each read event to

the write event that justifies it. We assume that jf is functional and complete: for each read

event there exists a unique write event that justifies it.

- $ew \subseteq [W]$ ;  $(cf \cap =_{loc} \cap =_{val})$ ; [W] is the *equal-writes* relation which relates conflicting writes that are considered equal. Its reflexive-transitive closure  $ew^*$  is an equivalence relation on write events.

- co ⊆ [W]; (=loc \ ew\*); [W] is the *coherence* order, a strict partial order that relates non-equal write events at the same memory location. Intuitively, it denotes the global order in which operations to the same memory location become visible to all threads.

Given an event structure *S*, we write *S*.*X* to refer to the *X* component of *S*. When *S* is clear from the context, we occasionally omit the "*S*.".

As an example, Fig. 3 depicts an event structure of LB. We can see, for example, that the events  $e_{11}^1 \rightarrow e_{21}^1$  form a branch of the first thread where the load corresponding to the instruction  $r_1 := x$  is justified by initial write. A conflicting branch  $e_{12}^1 \rightarrow e_{22}^1$  is shown on the right. Note that we only depict immediate conflict edges. For example, we draw  $e_{11}^1 \cdots e_{12}^1$ , but not  $e_{11}^1 \cdots e_{22}^1$ , as the latter can be derived. All reads have a corresponding write that justifies them, i.e., we have, init  $\stackrel{\text{jf}}{\rightarrow} e_{11}^1$   $e_{21}^1 \stackrel{\text{jf}}{\rightarrow} e_1^2$ , and  $e_2^2 \stackrel{\text{jf}}{\rightarrow} e_{12}^1$ . The two writes to location y are considered equal  $e_{21}^1 \stackrel{\text{ew}}{\rightarrow} e_{22}^1$ .

Definition 3.3. An execution graph G is a conflict-free event structure:  $G.cf = \emptyset$ .

PROPOSITION 3.4. For an execution graph G, we have:

- *G.*po *is total on the events of a given thread;*

- *G.*ew is the empty relation;

- G.co is total on same-location writes.

Next, we discuss how to extract an execution graph from an event structure. To do so, it is not sufficient to just take a conflict-free subset of events. For example, taking the single event  $\{e_{12}^1\}$  from the structure in Fig. 3 does not form an execution graph corresponding to the program LB. In addition, we must take all po-predecessors of the event and the writes that justify them. There is, however, one subtle point. Event  $e_1^2$  is justified by  $e_{21}^1$ , which is in conflict with  $e_{12}^1$ ; thus, instead of  $e_{21}^1$ , we pick the equivalent write  $e_{22}^1$ . To achieve that, we define the derived *reads-from* relation  $\mathsf{rf} \triangleq (\mathsf{ew}^* \; ; \; \mathsf{jf}) \setminus \mathsf{cf}$  by extending the  $\mathsf{jf}$  relation to  $\mathsf{ew}^*$  equivalence classes.

Definition 3.5. A justified configuration C of the event structure S is a subset of its events  $C \subseteq S$ .E, s.t.

- *C* is conflict free:  $\mathbf{cf} \cap C \times C = \emptyset$ ;

- C is closed w.r.t. po-prefixes:  $dom(po; [C]) \subseteq C$ ;

- *C* is rf-complete:  $C \cap R \subseteq rng([C]; rf)$ .

*Definition 3.6.* An execution graph *G* is *extracted from* an event structure *S*, denoted as  $S \triangleright G$ , if *G*.E is a justified configuration of *S* s.t.  $G.x = S.x|_{G.E}$  for  $x \in \{po, ew, co\}$  and  $G.jf = G.rf = S.rf|_{G.E}$ .

*Definition 3.7.* The *behavior* of an execution graph G, denoted as  $\mathcal{B}(G)$ , is a mapping assigning to each location x its final value, that is, the value written by the co-maximal write to x in G.

For example, in Fig. 3 the set of events marked by  $\bigcirc$  forms a justified configuration and thus induces an execution graph with the behavior  $\{x \mapsto 1, y \mapsto 1\}$ .

#### 3.1 Weakestmo Consistency

To filter out nonsensical event structures, Weakestmo defines a number of *consistency constraints*, which depend on the following auxiliary definitions.

- hb ≜ (po ∪ sw)<sup>+</sup> *Happens-before* is the transitive closure of the program order and *synchronizes-with* relations. The latter connects synchronized events. For example, it connects two fences if there exists a po; rf; po path between them.

- $\operatorname{ecf} \triangleq (\operatorname{hb}^{-1})^?$ ;  $\operatorname{cf}$ ;  $\operatorname{hb}^?$  Extended conflict propagates the conflict relation along hb.

- $eco \triangleq (co \cup rf \cup rf^{-1}; co)^+ Extended$  coherence is almost a total order on accesses to a given location; it orders every pair of such accesses except for equal writes, and reads reading from the same write.

- $jo \triangleq (jf \setminus po); (po \cup jf)^* Justification order$ . The jo predecessors of an event e are all the writes that cause the event e indirectly through some inter-thread communication. We call these writes the *justification set* of the event e.

- A write event w is a *promise* w.r.t. an event e if  $\langle w, e \rangle \in \mathsf{cf} \cap \mathsf{jo}$ . Additionally:

- if  $\langle w, e \rangle \in e^+$ ; po? then w is a certified promise;

- if  $\langle w, e \rangle \notin ew^+$ ; po? then w is a pending promise.

Consider Fig. 3 again. Write event  $e_{21}^1$  is a pending promise w.r.t.  $e_{12}^1$  and a certified promise w.r.t.  $e_{22}^1$ . The later event is exactly the equal write that certifies the promise.

Definition 3.8. Event structure S is Weakestmo-consistent if the following conditions hold.

```

• ecf is irreflexive. (NON-CONTRADICTORY)

• jf \cap ecf = \emptyset (Well-Justified)

• po \cup jf is acyclic (NO-THIN-AIR)

• hb; eco^2 is irreflexive. (COHERENT)

• [F]; po; ew^+ \subseteq po (Well-Fenced)

• cf \cap jo \subseteq ew^+; (po \cup po^{-1})^2 (CERTIFIED)

```

Fig. 4. Weakestmo2 inconsistent event structure of LBF-CEX.

•

$$ew \subseteq (cf \cap (jo \cup jo^{-1}))^+$$

(GROUNDED)

The first two constraints forbid nonsensical event structures where some event either is in conflict with itself, or justifies a conflicting event. NO-THIN-AIR prevents the values of reads to appear out-of-thin-air. Coherent enforces the *coherence* property at the level of the whole event structure<sup>1</sup>. The last three axioms are related to promises and certification: Well-fenced prevents promises to be issued across fences; Certified ensures that all promises are eventually certified; and Grounded guarantees that the ew relation is only used to certify promises, and not to link arbitrary writes.

Definition 3.9. Execution graph G is Weakestmo-consistent if there exists Weakestmo-consistent event structure S s.t. G can be extracted from S.

# 3.2 Weakestmo2 Consistency

As already mentioned in §2.2.1, Weakestmo-consistency guarantees neither LBRF<sub>RC11</sub> nor CL. For example, Figure 4 depicts a Weakestmo-consistent event structure of LBF-CEX that justifies the weak outcome  $r_1 = 1$ , which is forbidden by LBRF<sub>RC11</sub>.

In order to get the cyclic execution of LBF-CEX, Thread 2 first issues the promise  $e_{22}^2$ . Through Thread 3, this promise justifies another branch of Thread 2, namely  $e_{11}^2 \rightarrow e_{21}^2 \rightarrow e_{31}^2$ , and can be certified thanks to the equivalent write  $e_{31}^2$ . The problem is that in the two branches of Thread 2, the read of z is justified by two different writes. In other words, Thread 2 *baits* other threads with the promise, assuming that read of z gets value 0, but then *switches* by picking value 1 for this read.

To forbid this kind of behavior, we place an additional consistency constraint enforcing CL. We say that a write w externally justifies a read r if it justifies r and does not happen-before r nor justifies some other read that happens before r. For example, in Fig. 4,  $e_1^1$  externally justifies  $e_{11}^2$  and  $e_2^3$  externally justifies  $e_{21}^2$ . We require that whenever an event structure contains two conflicting branches due to some promise, the external justifications of the two branches agree modulo the external justification that created the conflict between the branches.

*Definition 3.10.* An event structure *S* is Weakestmo2-*consistent* if it is Weakestmo-consistent and also:

•

$$(jf \setminus (jf^?; hb))$$

; po;  $ew \subseteq jf$ ;  $(po \cup lbpat)$  (NO-BAIT-AND-SWITCH) where  $lbpat \triangleq cf_{imm}$ ;  $[rng(jf \cap (jf^?; hb))]$ ; po denotes the *load buffering pattern*.

<sup>&</sup>lt;sup>1</sup>To see why coherence is enforced for the whole event structure rather than on per-execution basis consult Chakraborty et al. [2019, §2.3].

<sup>&</sup>lt;sup>2</sup>The full version of the model (see ??) filters out executions that violate atomicity of read-modify-write operations or sequential consistency of sc accesses.

(a)  $e_{i+1}$  is in the middle of the certification branch. (b)  $e_{i+1}$  is the first event of the certification branch.

Fig. 5. Illustration to the proof of the LBRF theorem.

An execution graph is Weakestmo2-consistent if it can be extracted from some Weakestmo2consistent event structure.

The NO-BAIT-AND-SWITCH axiom requires that external justifications of one branch either also justify some read in the conflicting branch (jf;po) or be the very reason why the branch was created (jf; lbpat): the externally justified read should be in immediate conflict with a non-externally justified read heading the other branch.

Due to this axiom, the event structure of Fig. 4 is not Weakestmo2-consistent because event  $e_2^3$ externally justifies  $e_{21}^2$  but does justify any event po-before  $e_{22}^2$ . In contrast, the event structure of Fig. 3 is Weakestmo2-consistent. The only relevant external justification is that of  $e_{12}^1$  by  $e_2^2$ , which is allowed because  $e_{12}^1$  is in immediate conflict with  $e_{11}^1$ , which is po-before  $e_{21}^1$ .

# 3.3 Load Buffering and Data Race Freedom

We recall the definition of RC11-consistency and show that Weakestmo2 satisfies LBRF<sub>RC11</sub>.

*Definition 3.11.* An execution graph *G* is RC11-consistent if the following hold:

- po∪rf is acyclic (NO-THIN-AIR) • hb; eco? is irreflexive. (COHERENT)

THEOREM 3.12. Weakestmo2 satisfies LBRF<sub>RC11</sub>. (See [Moiseenko et al. 2022, p. D] for the full

PROOF SKETCH. We introduce a subclass of *promise-free* event structures for which  $cf \cap jo = \emptyset$ holds. It is easy to show that for Weakestmo2-consistent promise-free event structure S justifiedfrom relation coincides with reads-from relation: S.jf = S.rf. Therefore every extracted execution of a consistent promise-free event structure is RC11-consistent, since po∪rf acyclicity follows immediately from po ∪ jf acyclicity. Thus it suffices to show that every Weakestmo2-consistent event structure of an LB-race-free program is promise-free.

The latter can be shown by induction on the construction of an event structure. That is, given a Weakestmo2-consistent event structure S one can consider a sequence of events  $\{e_1, \dots, e_n\}$  of S ordered according to some total order extending  $(S.po \cup S.jf)^*$ . It is possible to construct S step-by-step by adding single event at each step. Then by induction we can show that each event structure  $S_i$  obtained on *i*-th step is promise-free.

Trivially, empty event structure  $S_0$  is promise free. Also it can be shown that if the event added on i+1 step  $e_{i+1}$  is a write or a fence, then the relation  $cf \cap jo$  cannot increase and thus the event structure remains promise-free. The only non-trivial case is when  $e_{i+1}$  is a read event.

This situation is depicted in Fig. 5a. We have a newly added read event  $e_{i+1}$  and a promise p. Read events r and r' are the first events at which two branches of the event structure diverge and become conflicting. The constraint NO-BAIT-AND-SWITCH guarantees that the read  $e_{i+1}$  cannot observe promise p in the middle of the certification branch, thus it has to be that  $e_{i+1} = r'$  (see Fig. 5b). Then it is easy to see that events r and w form a load-buffering race. Both of these events belong to the event structure  $S_i$  obtained on the previous step. Because of our inductive assumption,  $S_i$  is promise-free. Thus we can extract an RC11-consistent execution containing a load-buffering race, contradicting our assumption that P is LB-race-free under RC11. Therefore, it has to be that  $S_{i+1}$  remains promise-free.

Composing LBRF<sub>RC11</sub> with RC11's DRF<sub>SC</sub> theorem, we get DRF<sub>SC</sub> for Weakestmo2.

COROLLARY 3.13. Weakestmo2 satisfies DRF<sub>SC</sub>.

# 3.4 Soundness of Compilation Mappings

One of the main objectives of the advanced multi-execution weak memory models is to enable efficient compilation mappings to the hardware architectures. In this section, we show that our modification of the Weakestmo preserves this property. We prove soundness of the optimal compilation schemes, i.e., those that do not require to insert fences or fake dependencies when compiling relaxed accesses, from Weakestmo2 to memory models of x86, ARMv7, ARMv8, and POWER.

To achieve this goal, we adjust the proof of the compilation correctness for Weakestmo by Moiseenko et al. [2020]. The proof uses the IMM model as a mediator between Weakestmo and the hardware models. Since the correctness of compilation mappings from IMM to hardware models is already established by Podkopaev et al. [2019], it suffices to show correctness of compilation from Weakestmo2 to IMM, which boils down to the following statement [Moiseenko et al. 2020, § 2.3].

THEOREM 3.14. Let P be a program, and G be an IMM-consistent execution graph of P. Then, there exists an Weakestmo2-consistent event structure S of P such that  $S \triangleright G$ .

(See [Moiseenko et al. 2022, F] for the full proof.)

PROOF SKETCH. To prove the theorem, following the original proof, we construct the required event structure S step by step following a *traversal* of the IMM graph G [Podkopaev et al. 2019, § 6.2]. Traversal of the graph G induces operational small-step semantics  $G \vdash TC \xrightarrow{e} TC'$  where TC and TC' are *traversal configurations* and e is an event being traversed. Traversal configuration is a tuple  $\langle C, I \rangle$ , where  $C \subseteq G$ . E is a set of *covered events* and  $I \subseteq G$ . E is a set of *issued writes*.

Intuitively, covering an event corresponds to in-order execution of an instruction of the program, while issuing a write corresponds to our-of-order speculative execution of some store. An event can be covered whenever (i) all of its po predecessors are covered and (ii) it is already issued or it reads from an issued write. In order to issue a write, one must first issue all the writes of other threads on which it depends via the preserved program order ppo. These constraints can be manifested as the following invariants of the traversal configuration  $\langle C, I \rangle$ :

```

dom(po; [C]) \subseteq C C \cap W \subseteq I dom(rf; [C]) \subseteq I dom((rf \setminus po); ppo; [I]) \subseteq I

```

Giving the operational semantics of traversal  $G \vdash TC \xrightarrow{e} TC'$ , and the operational semantics of event structure construction  $S \xrightarrow{e} S'$  the proof then proceeds using the standard *simulation* argument. As such, the main challenge of our modification of the proof was to show that the new axiom NO-BAIT-AND-SWITCH is preserved during the simulation. It turned out that in order to ensure that we need to slightly modify the construction from Moiseenko et al. [2020].

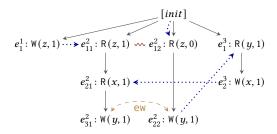

We demonstrate the problem with the original construction and our key idea on how to repair it with an example. Consider program LB-IMM in Fig. 6. Its annotated outcome is allowed by IMM and can be seen as a result of reordering the syntactically independent instructions of Thread 1.

To generate this outcome, the first step of the traversal issues W(a, 1) in Thread 1. To simulate this action, we create the branch  $e_{11}^1 \rightarrow e_{21}^1 \rightarrow e_{31}^1 \rightarrow e_{41}^1 \rightarrow e_{51}^1$  (see Fig. 6) using the *receptiveness* property [Podkopaev et al. 2019, § 6.4]. Receptiveness allows us to pick arbitrary values for intermediate

Fig. 6. LB-IMM and its partial Weakestmo2-consistent event structure.

read events in the branch if there is no dependency from these reads to the issued write. For each such read, we choose some "stable" justification write [Moiseenko et al. 2020, § 4.3.1]. In this case, the stable justification writes happen to be the initialization writes (omitted on Fig. 6 for brevity).

The next steps in the traversal cover R(a, 1) and then issue and immediately cover W(x, 1) and W(y, 1) in Thread 2. To match these steps, we add events  $e_1^2 \rightarrow e_2^2 \rightarrow e_3^2$  to the event structure.

Subsequently, the traversal issues W(b,1). At this point, the construction of Moiseenko et al. [2020] adds a branch  $e_{22}^1 \rightarrow e_{33}^1 \rightarrow e_{43}^1 \rightarrow e_{53}^1$ . It does so by picking suitable justification writes *for all reads* on which the issued write W(b,1) depends (via ppo). However, changing justification for multiple reads at once in the new branch violates NO-BAIT-AND-SWITCH.

We repair the construction by showing that we can replace justification writes for G-ppopreceding reads incrementally one-by-one, constructing a series of certification branches, as shown in Fig. 6. That is, we first construct the intermediate branch  $e_{22}^1 \rightarrow e_{32}^1 \rightarrow e_{42}^1 \rightarrow e_{52}^1$ . Doing so satisfies NO-BAIT-AND-SWITCH because the new branch differs from the previous branch only at the point of immediate conflict:  $e_{21}^1 \leadsto e_{22}^1$ . Starting from this intermediate branch, it becomes possible to add the required branch  $e_{33}^1 \rightarrow e_{43}^1 \rightarrow e_{53}^1$  which now has the event  $e_{43}^1$  matching the issued write W(b, 1). The remaining part of the simulation process is not shown in Fig. 6 because it proceeds unchanged

The remaining part of the simulation process is not shown in Fig. 6 because it proceeds unchanged compared to Moiseenko et al. [2020]: first R(b, 1) is covered, then W(z, 1) is issued and covered, and finally all the events of Thread 1 are covered. The corresponding events are added to the event structure in a straightforward way to match these traversal steps, arriving at the final execution graph justifying the annotated outcome.

# 3.5 Soundness of Program Transformations

Another important objective of the advanced weak memory models is to justify source-to-source program transformations applied by optimizing compilers. We next discuss the implications of strengthening Weakestmo for their soundness. A transformation tr from a source program  $P_{\text{src}}$  to a target program  $P_{\text{tgt}}$  is sound if does not add any new behaviors. That is, for every Weakestmo2-consistent execution  $G_{\text{tgt}}$  of  $P_{\text{tgt}}$ , there exists some Weakestmo2-consistent execution  $G_{\text{src}}$  of  $P_{\text{src}}$  with the same behavior:  $\mathcal{B}(G_{\text{src}}) = \mathcal{B}(G_{\text{tgt}})$ .

In [Moiseenko et al. 2022, G], we took the results of Chakraborty et al. [2019, §6.2] for the original version of Weakestmo and showed that all sound **reorderings** and **eliminations** of relaxed loads and stores **remain sound** for Weakestmo2. As an example of our reasoning we give a proof sketch for the soundness of the load/store reordering.

THEOREM 3.15. The reordering of two adjacent independent instructions  $a = (r_1 := x)$  and  $b = (y := r_2)$  is a sound source-to-source transformation.

Fig. 7. A fragment of the event structure construction that justifies load/store reordering.

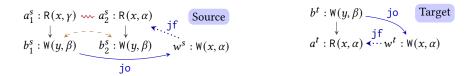

PROOF SKETCH. The proof proceeds by induction on the construction of the target event structure using the simulation argument of Chakraborty et al. [2019, §F]. Given a Weakestmo2-consistent execution graph  $G_{\rm tgt}$  of  $P_{\rm tgt}$ , we consider event structure  $S_{\rm tgt}$ , s.t.  $S_{\rm tgt} \triangleright G_{\rm tgt}$ , and we built it incrementally from the initial event structure:  $S_{\rm init}(P_{\rm tgt}) \rightarrow^* S_{\rm tgt}$ . Following these steps, we will construct  $S_{\rm src}$  and the required graph  $G_{\rm src}$ .

To simulate the target event structure construction step  $S_{\text{tgt}} \xrightarrow{e} S'_{\text{tgt}}$ , if the event added, e, is **not** a result of executing instruction b or a, the source event structure can be augmented by adding the same event  $S_{\text{src}} \xrightarrow{e} S'_{\text{src}}$ .

Otherwise, let us consult Fig. 7. It depicts a fragment of the source (on the left) and target (on the right) event structures. The target event structure construction adds the event  $b^t: W(y,\beta)$  corresponding to the instruction b. In the source, however, one has to execute instruction a first. In doing so, it might be not possible to add an event with the label  $R(x,\alpha)$  that will be added later in the target event structure. The corresponding justifying write event might have yet been added to the source event structure because it may, in turn, depend on the write event added as a result of executing b itself (see events  $b^t$  and  $w^t$  in the target event structure).

The construction of Chakraborty et al. [2019, §F] therefore creates an auxiliary execution branch in the source event structure consisting of events  $a_1^s$  and  $b_1^s$ . The construction justifies the  $a_1^s$ :  $R(x, \gamma)$  event by choosing the  $S_{src}$ .co-maximal non-conflicting write from  $S_{src}$ .jf?;  $S_{src}$ .hb prefix of  $a_1^s$ . Since instructions a and b are assumed to be independent, the choice of the value  $\gamma$  for the read  $a_1^s$  cannot affect the value of the write  $b_1^s$ :  $W(y, \beta)$ .

The construction then proceeds by adding events to the target and source event structures until the target reaches the event  $a^t$ . At this point, the construction adds another branch to the source consisting of events  $a_2^s$  and  $b_2^s$ . Now, the event  $a_2^s$  can have the required label  $R(x,\alpha)$  because there is already a justifying event  $w^s$  in the source event structure matching the target's justification event  $w^t$ . Finally, the write  $b_2^s$  is announced to be equal to  $b_2^s$ .

What remains to be shown is that the two conflicting branches  $a_1^s \rightarrow b_1^s$  and  $a_2^s \rightarrow b_2^s$  satisfy the axiom NO-BAIT-AND-SWITCH. Indeed, they only differ at the point of the immediate conflict, and moreover, the read  $a_1^s$  is justified from a  $(S_{\text{src.}} jf^?; S_{\text{src.}} hb)$ -preceding write.

#### 4 WMC: WEAKESTMO2 MODEL CHECKING

In this section, we present WMC, our model checking algorithm for Weakestmo2, which we build on top of GenMC [Kokologiannakis et al. 2019], an existing state-of-the-art, open-source stateless model checker for RC11 programs. Our algorithm is largely parametric in the underlying memory model, and so can in principle be adapted to other multi-execution memory models satisfying LBRF and CL. We proceed with a brief description of how GenMC operates under RC11 (§4.1), and then describe our extensions for Weakestmo2 (§4.2).

#### **Algorithm 1** Main exploration algorithm 1: **procedure** Visit( $P, G, \Pi$ ) if $\neg cons_{RC11 \setminus porf}(G)$ then return **switch** $a \leftarrow \text{next}_{P,\Pi}(G)$ **do** 3: case $a = \bot$ 4: if $\Pi = \emptyset$ then output "Exec OK" 5: case $a \in error$ 6: exit("Erroneous execution") 7: case $a \in R$ 8: for $w \in GetRFs(G, \Pi, a)$ do 9: Visit(P, SetRF(G, w, a), $\Pi$ ) 10: case $a \in W$ 11: $\Pi' \leftarrow \{\langle w, G_w \rangle \in \Pi \mid w \neq a \}$ 12: $Visit(P, G, \Pi')$ 13: 14: VisitRevisits $(P, G, \Pi, \Pi', a)$ otherwise Visit $(P, G, \Pi)$ 15: 1: **function** GetRFs(G, $\Pi$ , r) $W \leftarrow G.W_{loc(r)}$ if $\Pi \neq \emptyset$ then 3: $L \leftarrow \{w' \mid \exists \langle w, G' \rangle \in \Pi.$ 4: $\langle w', w \rangle \in G'.rf^?; G.hb$ $W \leftarrow W \cap L$ 5: return W

```

Algorithm 2 Exploration of revisits

1: procedure VisitRevisits(P, G, \Pi, \Pi', a)

if \Pi' \neq \emptyset then \langle Rs, \Pi_c \rangle \leftarrow \langle \emptyset, \emptyset \rangle

▶ In cert

else if \Pi \neq \emptyset then

▶ Cert OK

\langle Rs, \Pi_c \rangle \leftarrow \langle CERTREVS(G, a), \{a\} \rangle

4:

▶ Normal exec

5:

\langle Rs, \Pi_c \rangle \leftarrow \langle GETREVS(G, a), \emptyset \rangle

6:

for \langle w, r \rangle \in Rs do

7:

G' \leftarrow \text{Restrict}(G, r, w) \backslash rng([r]; G.po)

8:

9:

\Pi' \leftarrow \text{Promises}(G, r, \{w\} \cup \Pi_c \cup \text{InCyc}(G, r))

Visit(P, G', \Pi')

10:

1: function GetRevs(G, a)

return \{\langle a, r \rangle \mid r \in (G.\mathsf{T}_{\mathsf{loc}(a)} \setminus dom(G.\mathsf{porf}; [a]))

\cup dom(G.lbrace; [a])

1: function Promises(G, r, S)

return \{\langle w', G \rangle \mid \langle r, w' \rangle \in G.po; [dom(G.rfe)] \}

\land w' \in dom(G.porf; [S])

1: function CertRevs(G, e)

return \{\langle r, w \rangle \mid \langle r, e \rangle \in \text{po } \land G.rf; [r] \subseteq G.rf^?; G.hb

\land w \in G.W_{loc(r)} \} \cup

\bigcup_{w \in dom([W]:G,Do:[e])} GetRevs(G,T,w)

```

# 4.1 GENMC: Model Checking under RC11

GENMC, like other *dynamic partial order reduction* (DPOR) algorithms [Abdulla et al. 2014; Flanagan et al. 2005], verifies a program by enumerating its executions one at a time, while recording alternative exploration options along the way. This high-level procedure is depicted in Algorithm 1. (The highlighted code represents our extensions for Weakestmo2 and can be ignored for now.)

GenMC's Visit procedure explores all consistent executions of a program P under RC11<sup>3</sup> recursively. During the exploration, Visit maintains the current exploration graph G which is augmented with a *revisit set G*.T that records all reads in G whose reads-from edge can be changed. Initially, Visit is called with an empty execution graph.

At each step, as long as the current graph remains consistent (Line 2), VISIT picks the next event to add, and adds it to the graph using the next function (Line 3).

The role of next is twofold: it schedules a thread t and also adds the next event of t in the graph. If no thread can be scheduled (e.g., if all threads are finished), then the execution is complete, and next returns  $\bot$  (Line 4). If an error is encountered (e.g., if an assertion in the program is violated), next returns the error token error (Line 7). Otherwise, it returns the event it added a.

If a is a read, VISIT has to consider all possible rf edges for it. To that end, for each possible rf option w (given by Getres), VISIT recursively calls itself with the graph recording that a read from w (Lines 9 and 10).

If a is a write, apart from simply recursing further (Line 13), VISIT has to also check whether w can *revisit* any of the existing reads in G. This is necessary because, when a read r is added to the graph, it may well be the case that some write from which r could also read from has not yet been

<sup>&</sup>lt;sup>3</sup>Adapting the algorithm for a different model m merely requires changing the consistency check in Line 2 of Algorithm 1.

added to the graph. Thus, whenever VISIT adds a write *a*, it also checks whether any of the existing reads can be revisited to read from *a*, and explores these options via VISITREVISITS (Line 14).

Otherwise, VISIT simply recurses further.

*The VisitRevisits Procedure.* The calculation of revisitable reads is performed by VisitRevisits, by means of GetRevs. As can be seen in Algorithm 2, GetRevs returns a set where *a* is paired with all revisitable reads to the same location that are not in its porf prefix.

Subsequently (and in accordance to standard DPOR approaches), for each such revisit pair  $\langle r, w \rangle$ , VisitRevisits first restricts G (Line 8) so that it only contains the events that were added before r, as well as the events that are porf-before w (as w was added after r). Analogously, it restricts G. To so that it only contains reads added before (and including) r. Finally, VisitRevisits simply calls Visit recursively to generate the corresponding executions.

*GENMC:* An Example. Let us now illustrate how GENMC works with an example. Consider a variant of the load buffering program from §1 with no dependencies between instructions.

$$r_1 := x \mid r_2 := y$$

$y := 1 \mid x := 1$  (LB-NODEP)

We choose this example because it has 3 consistent executions under RC11 (Figures 1a to 1c) and one additional execution under Weakestmo2. Running GenMC on LB-NODEP highlights the difficulties arising when trying to enumerate the executions of programs with porf cycles. In the presentation below, we omit the values read by reads in the graphs, as they can be deduced from the rf edges.

GENMC starts with an empty graph and then adds two events corresponding to  $r_1 := x$  and y := 1, respectively, as can be seen below.

$$\begin{array}{cccc} \textbf{0} & [init] & \textbf{1} & [init] & \textbf{2} & [init] \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ &$$

Note that, because there are no other reads-from options for R(x) except for 0, the loop in Line 9 in Visit will only add one child node to the recursion tree. Similarly, because there are no revisit options for W(y, 1), VisitRevisits is not executed, and GenMC only calls Visit in Line 13 for the newly added write.

However, when the read event corresponding to  $r_2 := y$  is added in the next step, Visit starts two recursively explorations: one where R(y) reads 0, and an alternative one where it reads from W(y, 1). Let us assume that Visit first proceeds with the one where R(y) reads 0.

In a similar manner, when the write corresponding to x := 1 is added to the graph, Visit will initiate two recursive explorations: one where W(x, 1) does not revisit any reads, and one where it revisits R(x). Indeed, because R(x) is *not* porf-before W(x, 1), it will be considered by Getres, and VisitRevisits will initiate a recursive exploration.

In the non-revisiting case, the graph is complete (corresponding to Fig. 1a), so let us focus on the revisiting case. The graph created for the revisiting exploration is graph (5) below.

In effect, this graph models a scenario where the W(x, 1) was added just before the R(x): the only events that are present in the graph are the ones added before R(x) (i.e., the read itself), as well as those that are absolutely necessary in order to trigger W(x, 1) (here, its po-predecessor). Had we only kept the events that were added before R(x) when revisiting (as VISIT does in the read case), W(x, 1) would not existed upon restriction, and R(x) would not have been able to read from it.

Continuing with the revisiting case, W(y, 1) is added once again to the graph. This time, however, it does not revisit R(y), as the latter is both porf-before W(y, 1), and also not revisitable (recall that T is restricted to only contain events that were added before R(x)). The graph is now complete again (corresponding to Fig. 1c), and thus VISIT backtracks and explores the alternative rf for R(y).

The final exploration can be seen below. Since the recursive call corresponding to  $\bigcirc$ 7 was initiated by the addition of R(y), graph  $\bigcirc$ 7 is identical to  $\bigcirc$ 3 with the only exception being R(y)'s rf edge.

In the final step of the algorithm, VISIT adds W(x, 1) again in the graph. Since R(x) is porf before W(x, 1), no reads are considered by GetRevs, and the final exploration is concluded (cf. Fig. 1b).

# 4.2 WMC: Model Checking under Weakestmo2

We just saw how GenMC explores all three RC11-consistent executions of the LB program. When it comes to generating the execution of Fig. 1d, however, GenMC fails, for two major reasons.

First, GetRevs does not return reads that are porf-before the revisiting write. As such, even though W(y, 1) (resp. W(x, 1)) could revisit R(y) (resp. R(x)) in executions 6 and 8 to obtain the cyclic execution, that was impossible due to a porf-path between the read and the write.

Second, revisiting porf-earlier reads (which would seemingly solve the first issue above) is not enough on its own, as such reads may be non-revisitable (as e.g., R(y) in (6)).

We next show how WMC overcomes these difficulties and generates the execution of Fig. 1d, using the ideas of §2.4. Our WMC extensions are highlighted in Algorithms 1 and 2.

4.2.1 WMC: Overview. In order to generate LB behaviors, the first thing that needs to be changed is the function GetRevs(G, a). Besides the revisitable reads that are not porf-before a (as in GenMC's case), WMC also returns any reads that are porf-before a, as long as they are in an LB race with a:

$$\texttt{lbrace} \triangleq ([\texttt{R}] \; ; =_{\texttt{loc}} \; ; [\texttt{W}]) \cap (G.\texttt{rpo} \; ; \; (G.\texttt{rf} \; \backslash \; G.\texttt{po}) \; ; \; G.\texttt{porf})) \; \backslash \; (\texttt{hb} \cup \texttt{hb}^{-1})$$

Put differently, Getrevs tries to create executions with LB cycles only when an LB race is detected. That said, simply revisiting porf-prior events is not a sound way of generating executions with LB cycles. The problem is that when a write w revisits a porf-earlier read r, the graph that Restrict would create also includes r's po-suffix. This po-suffix has to be removed from the graph, since its very existence may depend on the value read by r (e.g., due to control flow). Yet, some events of the po-suffix do need to be re-added in the graph if porf-cyclic executions are to be generated.

WMC resolves this problem with a two-step approach. As a first step, when a write w revisits a porf-earlier read r, WMC removes the porf-prefix of w that is po-after r (Line 8). The writes that are po-after r and are read externally are kept in a *promise set* calculated by Promises (Line 9),

which is in turn used during the recursive exploration (Line 10). Promise sets,  $\Pi$ , are sets of pairs consisting of the write that is promised and the execution graph when the promise was issued (the latter is used to constrain the reads within promise certifications).

As a second step, whenever VISIT encounters a non-empty promise set, WMC initiates a *certification phase*. During this phase, WMC operates in a restricted mode: all promises of  $\Pi$  have to be fulfilled (i.e., the corresponding writes have to be re-added to the graph), and all non-local explorations (see §2.3) are postponed until the certification phase succeeds.

To that end, WMC modifies GENMC's original algorithm in the following ways.

First, the next function is changed so that when WMC is in a certification phase (i.e.,  $\Pi \neq \emptyset$ ), next returns the events of the thread under certification until either all promises have been fulfilled, or all the events of this thread have been added to the graph (in which case next returns  $\bot$ ).

Second, the GetrRFs function is modified to constrain the possible reads-from options during the certification phase (Line 3). The modified version of the function calculates the set of local writes that were used to issue promises (Line 4). Reading from these writes is safe, since it cannot lead to bait-and-switch behaviors. All other (non-local) reads-from options will be considered only after the certification procedure has succeeded (see below).

Third, VisitRevisits is changed to behave differently under certification. After Visit removes any promise in  $\Pi$  fulfilled by a (Line 12), VisitRevisits checks whether the certification is over. If the certification is not over yet, no revisits are performed (Line 2). (Analogously to Getres, a's revisits will be calculated later once the certification procedure completes successfully.) If the certification is over (i.e., all promises have been fulfilled), then all rf options that were discarded by Getres and all revisits that were skipped by VisitRevisits will now be considered (Line 4). To that end, VisitRevisits calculates all non-local options for the reads and writes of the thread that completed the certification (by means of Certres; Line 4), and then recursively explores them.

Arguably, the most intricate parts in the changes described above are (1) the calculation of non-local options at the end of a certification, and (2) the calculation of the promise set for a recursive exploration. But, before diving into these parts, let us see an example of WMC in action.

4.2.2 WMC: An Example. Using the modifications above, WMC explores all 4 executions of Fig. 1. Initially, the exploration remains the same as with GenMC. In graph 6, however (and in contrast to GenMC), WMC also considers R(y) to be revisited by W(y, 1), eventually leading to graph 2 below, where W(x, 1) needs to be certified:

Let us now see what happens when VISIT proceeds with exploration corresponding to graph ②. Since  $\Pi$  is non-empty, WMC enters a certification phase. The next event to be added is W(x,1), which fulfills the promised write of the first thread. Since no revisits were skipped (and no rf edges were restricted) during the certification phase, CertRevs returns the empty set, and the execution (corresponding to Fig. 1d) is complete.

The rest of the exploration proceeds in a similar manner. When WMC encounters graph (8), it will notice that graph (8) contains an LB race, and therefore generate another (duplicate) execution with the weak LB behavior<sup>4</sup>. In general, however, this is not something WMC could have predicted, and thus has no way of avoiding it without doing some extra bookkeeping (see below).

We conclude this example with two remarks.

<sup>&</sup>lt;sup>4</sup>The exploration is similar to the one presented for (2) above, and is thus omitted for brevity.

Blocked Executions. While in the LB-NODEP program above all promises could be fulfilled, this is not the case in general. In the LB+CTRL program below, whenever a read gets revisited in hope that a cyclic execution will be generated (as in execution ② above), its promise cannot be fulfilled because of the control dependency between the read and its subsequent write. Although there can be a fair number of blocked executions in a test case, the overhead that is induced on WMC by such explorations is modest because WMC does not fully explore these blocked executions: it discards them as soon as the certification phase fails.

$$\begin{array}{c|c} r_1 \coloneqq x \\ \textbf{if } r_1 = 0 \textbf{ then} \\ y \coloneqq 1 \end{array} \quad \begin{array}{c|c} r_2 \coloneqq y \\ \textbf{if } r_2 = 0 \textbf{ then } \text{ (LB+CTRL)} \\ x \coloneqq 1 \end{array} \quad \begin{array}{c|c} r_1 \coloneqq x \\ y \coloneqq 1 \end{array} \quad \begin{array}{c|c} r_2 \coloneqq z \\ x_3 \coloneqq y \\ x \coloneqq 1 \end{array} \quad z \coloneqq 2 \quad \text{ (RLB+W)}$$

Duplicate Executions. One may wonder what does WMC do about duplicate executions in general. For LB-race-free programs, WMC essentially follows GENMC: instead of exploring the executions of a program recursively, WMC uses a stack and some auxiliary structures that allow it to not encounter any duplication at the cost of some extra memory (see [Kokologiannakis et al. 2019]).

For LB-racy programs like LB-Nodep, however, it is not possible to avoid exploring duplicate executions simply by recording the LB cycles that have already been encountered in the exploration. Indeed, it turns out this naive approach of recording LB cycles is not sound, as it may lead to the disposal of valid executions. To see this, consider the RLB+W program above and assume that we record the encountered cycles. Note that RLB+W has two executions with LB cycles: one where  $r_2 = 0$ , and one where  $r_2 = 2$ . Assuming that events are added from left to right and that we first encounter the cyclic execution where  $r_2 = 0$ , when we encounter the second execution where  $r_2 = 2$ , it will be erroneously disposed, as it involves the exact same cycle as the one with  $r_2 = 0$ .

A sound way to avoid duplication is to record the whole porf-prefix of such LB cycles. Although this can amount to recording complete execution graphs, it does not induce a significant space overhead in practice because executions with LB cycles are rare.

4.2.3 WMC: Promises and Non-Local Revisits. Finally, let us now return to the last remaining parts of VISITREVISITS: the calculation of non-local options at the end of a certification, and the calculation of the promise set  $\Pi$ .

Starting with the calculation of non-local options, when the certification is over, we have to a) calculate alternative rf edges for the reads that read locally during certification, and b) calculate revisits for writes the revisits of which were skipped during certification. As can be seen in Algorithm 2, CertRevs performs exactly these two actions.

Continuing with the calculation of the promise set, given a revisit  $\langle w, r \rangle$ , the definition of Promises simply returns the writes after po-after r that are read externally, and are porf-before its last parameter S.

The only question that remains the be answered is *what* should be passed as the *S* argument of Promises (cf. Visitrevisits, Line 9). Clearly, one thing that should be passed as part of *S* is the revisiting write *w* indeed, this is the first component passed to Promises. Passing just *w*, however, is not enough. In fact, there are two more cases we have to take into account.

As an example of the first case, consider the end of a successful certification phase triggered by a revisit  $\langle w, r \rangle$ , as well as a revisit  $\langle w', r' \rangle$  returned by CertRevs at the certification end. Let us further assume that the revisit  $\langle w', r' \rangle$  initiates a new certification phase. In such cases, it is inadequate to consider as promises only the writes that are porf-before w'. Since w' is itself porf-before w (and part of the cycle that the revisit  $\langle w, r \rangle$  created), we also have to include w in S in order to ensure that w's cycle will be preserved; that is the role of S's second component,  $\Pi_c$ . (Note that revisiting r' from w' without preserving the cycle of  $\langle w, r \rangle$  is also possible, but that execution will be obtained in another graph without the  $\langle w, r \rangle$  cycle.)

As an example of the second case, consider the program below along with its Weakestmo2-consistent execution where all reads read 1:

$$z := 1 \quad \begin{vmatrix} r := z \\ s := x \\ \text{if } r = 0 \lor s = 1 \text{ then } \\ y := 1 \end{vmatrix} \quad a := y \\ x := a \quad \begin{cases} w(z, 1) & R(y, 1) \\ R(x, 1) & R(y, 1) \\ R(x, 1) & R(x, 1) \\ R(x, 1) & R$$